Микросхемы ПЛИС Speedster22i от Achronix: самые быстрые и самые большие. Часть 3

Порты ввода/вывода общего назначения (GPIO)

Типы портов ввода/вывода общего назначения

Количество входов/выходов у микросхем серии Speedster22i HD показано в таблице 1. В микросхемах Speedster22i входы и выходы могут быть разделены на пять категорий, как это видно в таблице 2.

|

Параметры |

HD680 |

HD1000 |

HD1500 |

|

В корпусе FBGA2601 (52,5×52,5 мм) |

– |

GPIO = 960 |

GPIO = 960 |

|

В корпусе FBGA1936 (45×45 мм) |

GPIO = 684 |

GPIO = 684 |

GPIO = 684 |

|

В корпусе FBGA1520 (40×40 мм) |

GPIO = 684 |

– |

– |

|

Наименование |

Описание |

Количество |

|

Программируемые I/O — расширенные возможности |

Программируемые пользователем. Совместимые с большим числом стандартов I/O. Скорости нарастания от медленных до средних. DLL применяется для корректировки задержек ввода и вывода, что требуется для работы памяти и каналов данных интерфейсов |

12×N, где N = числу байтовых линий (зависит от корпуса и от объема микросхемы) |

|

I/O для сериализаторов (SerDes) |

Программируемые пользователем. Совместимые с большим числом стандартов, работающих с SerDes. Высокие скорости нарастания |

Для пары линий: – 2×4 вывода для данных (Rx/Tx); – 1×2 вывода для опорной синхрочастоты (совместно используются линиями) |

|

I/O для синхросигналов (Clock) |

Эти I/O подключаются к Global Clock Generator в соответствующем углу микросхемы |

24 |

|

Выделенные (Dedicated) I/O |

Зарезервированы для тестирования и конфигурации микросхемы |

23 |

|

Питание/«земля» |

Питание ядра, питание I/O и «земля» |

Зависит от корпуса и от объема микросхемы |

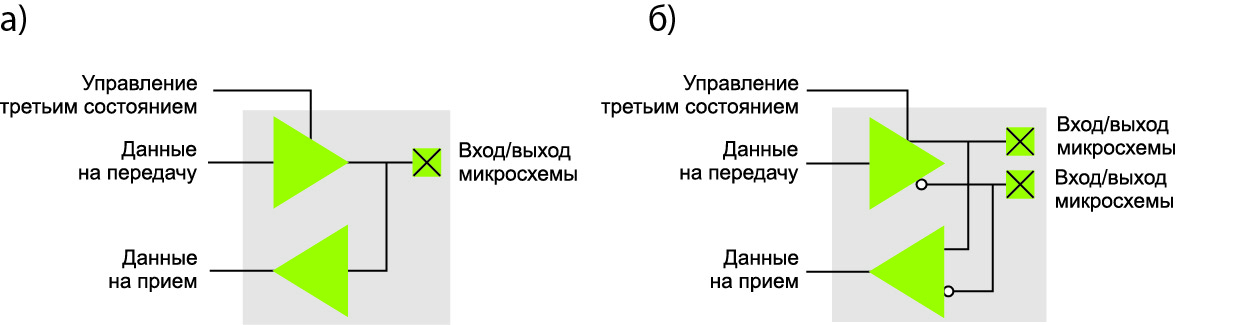

Каждый программируемый порт ввода/вывода может быть сконфигурирован так, чтобы соответствовать любому стандарту из большого числа стандартов ввода/вывода, как асимметричных, так и дифференциальных, как показано в таблице 3. Каждый ввод/вывод может работать как вход, выход или двунаправленный вход/выход (рис. 1). Конечно, дифференциальный сигнал использует два вывода I/O, тогда как сигнал асимметричный использует только один.

Рис. 1. Программируемые порты ввода/вывода:

а) асимметричный буфер приема-передачи данных;

б) дифференциальный буфер приема-передачи данных

|

Тип сигнала |

Напряжение, |

Класс |

Стандарт |

Максимальная частота |

Максимальная пропускная |

|---|---|---|---|---|---|

|

LVCMOS |

1,8 |

– |

– |

300 |

300 |

|

1,5 |

|||||

|

1,2 |

|||||

|

HSTL |

1,8 |

I |

QDR II SRAM/RLDRAM II |

533 |

1066 |

|

II |

|||||

|

1,5 |

I |

Memory and switch fabric |

|||

|

II |

|||||

|

SSTL |

1,8 |

I |

DDR SDRAM/RLDRAM II |

400 |

800 |

|

II |

|||||

|

1,5 |

I |

DDR2 SDRAM/FCRAM II |

533 |

1066 |

|

|

II |

|||||

|

POD |

1,8 |

– |

– |

400 |

800 |

|

1,5 |

|||||

|

LVDS |

1,8 |

– |

SPI4.2, SFI4.1 |

800 |

1600 |

|

Differential HSTL |

1,8 |

I |

QDRII SRAM/RLDRAM II |

533 |

1066 |

|

II |

|||||

|

1,5 |

I |

Memory and Switch Fabric |

|||

|

II |

|||||

|

1,2 |

II |

||||

|

Differential SSTL |

1.8 |

II |

DDR2 SDRAM |

533 |

1066 |

|

1,5 |

– |

800 |

1600 |

||

|

1,2 |

1066 |

2133 |

|||

|

HT 1.0 |

0,6 |

– |

– |

800 |

800 |

Банки входов/выходов состоят из байтовых групп линий (byte lane). Каждая байтовая группа линий содержит:

- 12 буферов входов/выходов, состоящих из 12‑битовых модулей. Каждая пара двух буферов I/O может быть сконфигурирована как два асимметричных буфера I/O или как один дифференциальный буфер I/O.

- 1 DLL, работающий как мастер, и 12 ведомых элементов задержки — по одному ведомому элементу задержки для каждого из битовых модулей.

- Для подключения памяти SDRAM DDR2/DDR3 имеются соответствующие логические и физические структуры для DQS.

- Логика указателя записи и указателя чтения для Meso-chronous синхронизатора.

- Мультиплексоры и буферы для сети синхрочастоты (Source Synchronous clock networks).

- 2 буфера ввода/вывода в каждой байтовой группе линий, которые могут получать сигналы синхрочастот от внешних устройств. Они могут использоваться в качестве одной дифференциальной пары (например, чтобы получить дифференциальный DQS для DDR2) или как два асимметричных буфера (например, чтобы получить CQ синхрочастоты и CQn для QDR2). Другие 10 буферов ввода/вывода могут применяться в качестве входов для данных, которые будут защелкиваться под полученные синхрочастоты.

- Логика в каждом разрядном модуле, чтобы поддерживать SDR, DDR и QDR в направлении ввода и вывода, плюс вывод разрешения для логики.

- В байтовой группе линий интегрируется VREF.

Банки портов ввода/вывода

Программируемые порты ввода/вывода в Speedster22i группируются в банки. Все порты ввода/вывода в одном банке должны совместно использовать:

- один VDDO;

- один VREF;

- один RREFs (используемый для контролируемого импеданса I/O).

Есть три типа I/O‑банков: банк EF, банк синхрочастоты и банк конфигурации (EF Bank, Clock Bank and Configuration Bank). На рис. 2 показано расположение банков в микросхеме. Число банков может изменяться в зависимости от объема ресурсов микросхемы.

Банк с расширенными функциями EF

Для начала определим термин ODT. Если необходимая для работы интерфейса резистивная терминация расположена не на системной плате, а находится непосредственно в микросхеме, то она называется On-Die Termination (ODT). А теперь вернемся к рассмотрению банков.

Банк EF (Enhanced Function) содержит:

- четыре группы байтовых линий или 48 портов ввода/вывода;

- общие калибровочные резисторы управления и калибровки PVT (давление, объем и температура) для импеданса драйвера;

- общие калибровочные резисторы управления и калибровки PVT (давление, объем и температура) для ODT параллельной терминации и ODT дифференциальной терминации;

- все буферы I/O используют общее напряжение ввода/вывода VDDO;

- все буферы I/O используют общее опорное напряжение VREF.

Есть три банка EF, соответствующих каждому контроллеру DDR2/3. Половина всех банков EF расположена на правой стороне устройства, другая половина расположена на левой.

Банк синхрочастоты

Банки синхрочастоты (Clock Bank) используются для приема сигналов синхрочастоты. Есть в общей сложности четыре банка синхрочастоты (один в каждом углу микросхемы), и в общей сложности имеется 24 входных контакта для синхрочастоты.

Банк синхрочастоты содержит:

- шесть буферов I/O для шести асимметричных сигналов синхрочастоты или трех дифференциальных сигналов синхрочастоты или любую комбинацию асимметричных и дифференциальных синхрочастот;

- все шесть буферов I/O используют общее напряжение VDDO для I/O;

- все шесть буферов I/O используют общее опорное напряжение VREF;

- в отличие от банков EF, банк синхрочастоты не имеет управления для калибровки PVT (давление, объем и температура).

Банк конфигурации (Configuration Bank)

Банк конфигурации представляет собой специальный I/O‑банк, который находится на нижней стороне микросхемы Speedster22i. Буферы I/O в этом банке используются для JTAG и интерфейсов конфигурирования и программирования. Общее количество буферов I/O в этом банке — 36.

Дифференциальные пары

Когда выводы используются в качестве дифференциальной пары, такой как LVDS, то контакты, имеющие четные номера в названии, будут положительными, а контакты с нечетным номером в названии (то есть у которых номер на единицу больше, чем у четного) считаются отрицательными. Например, контакт, имеющий наименование PAD_EN_BYTEIO0DQ2, будет положительным, а PAD_EN_BYTEIO0DQ3 соответственно отрицательным. Контакты, имеющие наименование *DQS, будут положительными, а *DQSn — отрицательными.

Ресурсы ячейки ввода/вывода

Если рассматривать порты ввода/вывода так, как это делалось у Altera и Xilinx, то можно сказать, что каждая ячейка программируемого ввода/вывода состоит из буферов ввода и вывода и логики, обеспечивающей связь этого буфера с ядром логики. То есть в одной ячейке есть ресурсы, отвечающие как за прием, так и за выдачу информации. Ячейка ввода/вывода состоит из трех логических блоков, которые и осуществляют подключение соответствующего буферного интерфейса ввода/вывода к ядру ПЛИС.

У компании «Акроникс» принята несколько другая терминология: ресурсы ячейки ввода/вывода рассматриваются как три отдельные части, отдельно для ввода данных и отдельно для вывода данных. Причем эти ресурсы компания «Акроникс» называет не «ячейка ввода/вывода», а «битовый модуль» (Bit-Module). Битовый модуль в ячейке ввода/вывода состоит из трех логических блоков, которые и осуществляют подключение соответствующего буферного интерфейса ввода/вывода к ядру ПЛИС. Далее будут описаны эти блоки.

Логика в приемной части тракта

В приемной части тракта, то есть в направлении от I/O‑буфера к ядру ПЛИС, есть специальные аппаратные средства, через которые и реализуется подключение выходной части I/O‑буфера к ядру ПЛИС. Входные данные могут дополнительно быть задержаны на элементе задержки прежде, чем они будут поданы в приемную логику в информационном канале. Битовый модуль в приемной части имеет три режима работы:

- Комбинаторный к ядру (Combinatorial to the core) — в этом режиме данные, приходящие из входного буфера, непосредственно передаются к ядру ПЛИС.

- SDR — в этом режиме данные, приходящие из входного буфера, защелкиваются в регистрах в битовом модуле, прежде чем они передаются к ядру ПЛИС.

- DDR — в этом режиме для каждого бита получаются двухбитовые данные — DDR, и они передается к ядру ПЛИС. У этого режима есть две версии:

- два бита передаются ядру ПЛИС на различных фронтах синхроимпульса;

- оба бита передаются ядру ПЛИС на одном и том же фронте синхроимпульса.

На рис. 3 показан битовый модуль в приемном тракте микросхемы HD1000.

Логика в передающей части тракта, передача данных

В передающей части тракта, то есть в направлении от ядра ПЛИС к I/O‑буферу, есть специальные аппаратные средства, через которые и осуществляется подключение входной части I/O‑буфера к ядру ПЛИС.

Битовый модуль в направлении передачи поддерживает три режима:

- Комбинаторный — в этом режиме данные, приходящие из ядра ПЛИС, непосредственно передаются к выходу буфера.

- SDR — в этом режиме данные, приходящие из ядра ПЛИС, защелкиваются в регистрах в битовом модуле, прежде чем они передаются к буферу вывода.

- DDR — в этом режиме два бита данных, приходящие из ядра ПЛИС, преобразовываются в данные DDR, прежде чем они передаются к буферу вывода.

В каждом из вышеупомянутых трех режимов информационный канал передачи может дополнительно включать элемент задержки. На рис. 4 показан битовый модуль в передающем тракте микросхемы HD1000, передача данных.

Все триггеры, показанные выше, могут быть сконфигурированы так, чтобы они запускались или положительным, или отрицательным запускаемым фронтом. Все триггеры поддерживают асинхронный или синхронный сброс. У них также есть общий вход разрешения. Когда эти триггеры снимаются со сброса, то их выход может быть или установлен в «1» или сброшен в «0».

Логика в передающей части тракта, передача сигнала разрешения выхода

У выходного тракта разрешения включения выхода (Output Enable) есть те же режимы работы, что и у передающей части тракта:

- Комбинаторный — в этом режиме сигнал разрешения, приходящий из ядра ПЛИС, идет непосредственно в буфер вывода.

- SDR — в этом режиме сигнал разрешения, приходящий из ядра ПЛИС, защелкивается в регистрах в битовом модуле, прежде чем передается к буферу вывода.

- DDR — в этом режиме два бита сигналов разрешения, приходящие из ядра ПЛИС, преобразовываются в данные DDR, прежде чем они передаются к буферу вывода.

На рис. 5 показан канал передачи сигналов разрешения для битового модуля в передающем тракте микросхемы HD1000. Все триггеры, показанные выше, могут быть сконфигурированы так, чтобы они запускались или положительным, или отрицательным фронтом синхросигнала. Все триггеры поддерживают асинхронный или синхронный сброс. У них также есть общий вход разрешения. Когда эти триггеры снимаются со сброса, их выход может быть или установлен в «1», или сброшен в «0».

Рис. 5. Канал передачи сигналов разрешения для битового модуля в передающем тракте микросхемы HD1000

Битовый модуль, элемент задержки

У каждого битового модуля есть свой элемент задержки (delay element), который может использоваться или в приемном информационном канале, или в передающем информационном канале. Величина задержки устанавливается в конфигурации или динамически во время работы. DLL используется как ведущий по отношению к элементу задержки. В элементе задержки может быть сформирован набор задержек разной длительности, зависимых от изменений PVT. Кроме того, при использовании DLL задержка может быть скорректирована с шагом в 1/64 периода опорной синхрочастоты DLL (рис. 6).

Как было сказано выше, элемент задержки может быть установлен не только по выходу, но и по входу. На рис. 7 показано, как можно производить задержку входных сигналов для требуемой обработки в проекте пользователя. А на рис. 8 представлено различие в работе элементов задержек для микросхем конкурентов и микросхем HD1000. Из приведенного рисунка видно, что для микросхемы HD1000 имеют больше возможностей для необходимой подстройки сигналов на элементах задержки.

В таблице 4 показаны параметры работы элемента задержки DLL.

|

Параметр |

Значение |

|---|---|

|

Диапазон частот для синхронизации |

311–1066 МГц |

|

Диапазон режима работы входной опорной частоты |

40–60% |

|

Число выводов на линию |

1 |

|

Число линий на мастера |

12 |

|

Регулировка задержки для ведомого |

0–100% от цикла опорной синхрочастоты |

|

Разрешение фазы выхода |

6 бит |

|

Точность фазы выхода |

±4% от цикла опорной синхрочастоты |

|

Максимальный джиттер за период с шумовой частотой 200 МГц и ±115 мВ синусоидальным шумом |

±2% peak-to-peak от цикла опорной синхрочастоты |

|

Минимальная длительность ведомого импульса для «1» и «0» |

25% от цикла опорной синхрочастоты |

|

Максимальное время захвата (Lock Time) |

<500 циклов опорной синхрочастоты |

Дополнительные ресурсы портов ввода/вывода

У битового модуля есть дополнительная логика для того, чтобы поддерживать функцию PHY для различных интерфейсов памяти (например, SDRAM DDR2/DDR3, QDR2 + SRAM) или для сетевых интерфейсов (например, SPI4.2) и других синхронных интерфейсов.

Температурный сенсор

Этот раздел не относится к программируемым портам ввода/вывода, но, тем не менее, куда-то все же нужно добавить текст о температурном сенсоре. Как и во всех серьезных микросхемах, в микросхемах Speedster22i есть диод, предназначенный для контроля температуры. Анод и катод этого диода соединяются с двумя выделенными выводами (TEMP_DIODE_P и TEMP_DIODE_N).

Обычно такой датчик температуры применяют в схеме контроля температуры и используют результат работы такой схемы в качестве критерия выбора, например:

- Выборочное отключение схемы, чтобы уменьшить потребляемую мощность.

- Выбор схемы включения какой-либо задержки, что позволяет достигнуть требуемого пользователем условия.

Архитектура SerDes 12,75 Гбит/с

Все микросхемы Speedster22i имеют встроенную поддержку SerDes, с помощью которой можно реализовать различные протоколы. Они представляют собой архитектуру с низкой потребляемой мощностью (<100 мВт в 10 Гбит/с) и способны работать со следующими скоростями передачи данных:

- 1,0625–12,75 Гбит/с;

- 531,25–1062,5 Мбит/с при использовании 2×-передискретизации (over-sampling);

- 265,625–531,25 Мбит/с при использовании 4×-передискретизации.

Семейство микросхем Speedster22i поддерживает до 64 полнодуплексных линий SerDes, каждая из которых может работать на скорости передачи данных в 12,75 Гбит/с, до шестнадцати SerDes на 28 Гбит/с. Каждый SerDes может использоваться для внутриприборной связи как по кросс-плате, так и для связи между микросхемами, находящимися на одной плате. Количество сериализаторов у микросхем серии Speedster22i HD показано в таблице 5.

|

Параметры |

HD680 |

HD1000 |

HD1500 |

|

В корпусе FBGA2601 (52,5×52,5 мм) |

– |

12G = 64 28G = 0 |

12G = 48 28G = 16 |

|

В корпусе FBGA1936 (45×45 мм) |

12G = 40 28G = 0 |

12G = 40 28G = 0 |

12G = 20 28G = 4 |

|

В корпусе FBGA1520 (40×40 мм) |

12G = 18 28G = 0 |

– |

– |

Расположение блоков SerDes в микросхеме Speedster22i показано на рис. 9. Блоки SerDes находятся на верхней и нижней сторонах микросхемы.

Блок SerDes, в свою очередь, состоит из следующих блоков: блока подуровня физического кодирования (PCS, Physical Coding Sublayer), блока присоединения к физической среде (PMA, Physical Media Attachment) (рис. 10), из интерфейса, связывающего блок подуровня физического кодирования с ядром логики, и из цепей синхронизации, отладки и тестирования.

Рис. 10. Блок-схема разделения трансивера на МАС и PHY и разделения PHY на блок подуровня физического кодирования и блок присоединения к физической среде

Блок PMA обрабатывает низкоуровневую сигнализацию данных, в то время как PCS выполняет функции контроллера интерфейса для заданного протокола обмена. Также PCS может обрабатывать и любое другое кодирование данных, которое потребуется разработчику.

Блоки PCS в SerDes могут работать в режиме PCIe, 10GBASE-R, Ethernet 1G и XAUI. У этого блока также есть некоторая поддержка других взаимосвязанных протоколов, работающих через PCS, таких как Interlaken, SPI4.2, Infiniband, Fiber-Channel, SAS/SATA, SONET, OC, OBSAI и CPRI. SerDes может быть соединен в ПЛИС с любыми встроенными аппаратными IP-блоками (PCIe, Interlaken, и 10/40/100G MAC) или подключен к логике ПЛИС для программной реализации любого другого поддерживаемого протокола.

Для работы SerDes требуется опорная синхрочастота, которую необходимо подключить к SerDes. Также надо отметить, что опорная синхрочастота SerDes должна появиться прежде, чем ПЛИС будет сконфигурирована. До конфигурации, в течение и после конфигурации эта опорная синхрочастота никогда не должна останавливаться или изменяться. Всякий раз, когда используется интерфейс SBUS по любой линии SerDes, синхрочастота этого интерфейса обязательно должна заработать до того, как микросхема ПЛИС будет сконфигурирована. До конфигурации, в течение и после конфигурации синхрочастота SBUS никогда не должна останавливаться или изменяться. Синхрочастота SBUS должна быть меньше 100 МГц и меньше опорной частоты синхрочастоты SerDes.

Блок присоединения к физической среде (PMA-Physical Media Attachment)

Блок присоединения к физической среде состоит из передающей части (Tx), приемной части (Rx), их общей части и цифрового РМА (DPMA, Digital PMA).

Общая часть блока PMA

Общая часть блока РМА состоит из следующих субблоков. Блок опорной синхрочастоты, который выполняет буферизацию и деление опорной синхрочастоты, прежде чем подать ее к синтезатору. Синтезатор — это PLL, который генерирует синхрочастоту для сериализатора передатчика. У него также есть встроенная схема, которая программно может быть включена для работы в режиме распределенного спектра (spread-spectrum clocking). Для каждой линии имеются свои аппаратные ресурсы с выделенным для них синтезатором частоты, причем для работы этих линий не требуются какие-либо компоненты вне кристалла.

Как для синтезатора частоты PLL, так и для восстановления данных и синхрочастоты CDR применяется полностью цифровая архитектура. Она имеет точность и низкий джиттер, как у аналоговой PLL, а диапазон настройки, как у цифровой PLL. Поддерживается 16‑разрядный дробный коэффициент умножения. Есть поддержка быстрого режима захвата (lock) для EPON/GPON.

Синхронизация осуществляется от внешней опорной частоты диапазона от 50–300 МГц или же от восстановленной синхрочастоты. На рис. 11 приведена блок-схема синтезатора.

Также имеется схема смещения, управляющая смещениями для всех аналоговых схем в PMA. Для тестов при производстве и при отладке используется встроенный аналоговый тестовый порт.

Передающая и приемная части

Блок Rx/Tx состоит из следующих субблоков. Буфер передатчика (Тх) преобразовывает асимметричный сигнал в дифференциальный и выполняет коррекцию (или предварительные искажения) исходящего последовательного сигнала. Буфер приемника (Rx) преобразовывает дифференциальный сигнал в однополярный асимметричный сигнал и выполняет коррекцию на входящем сигнале, используя входной драйвер с линейным эквалайзером длительного режима (CTLE, Continuous Time Linear Equalizer) и 5‑ступенчатым эквалайзером подстройки по обратной связи (DFE, Decision Feedback Equalizer). Может выполняться автокалибровка CTLE и DFE, причем для CTLE с усилением на 20 дБ, настраиваемым в диапазонах частот, используемых для передачи данных. Выходной драйвер имеет 4‑ступенчатый FIR-фильтр с эквалайзером «предподачи» (FFE, Feed Forward Equalizer).

Для приемника дифференциальное входное напряжение: 50–2000 мВп-п, для передатчика выходное дифференциальное напряжение 400–1500 мВп-п при скорости нарастания сигнала 31–170 пс. Поддерживается согласование линии по постоянному и по переменному току (AC and DC coupling). В микросхеме выполнена встроенная терминация точными резисторами 100 Ом и есть прозрачный калибровочный механизм, чтобы компенсировать изменение PVT.

Также из входящего сигнала при десериализации производится восстановление данных и синхрочастоты (CDR).

С помощью высокоскоростной синхрочастоты от синтезатора в блоке Rx/Tx выполняется преобразование параллельных данных в последовательные данные (Serializer/Deserializer). В приемной части имеется встроенный осциллоскоп, позволяющий графически изобразить глазковую диаграмму входящего сигнала (получаемого после коррекции в эквалайзерах) и производить просмотр ширины и высоты глазковой диаграммы, а также определять скорость появления ошибок (BER) для входящего сигнала.

Цифровой PMA (DPMA)

Блок DPMA состоит из следующих составных частей. Блок калибровки выполняет калибровку всех аналоговых схем, используя установки настройки и смещения. Блок самотестирования BIST PMA, который включает генерацию и проверку паттернов, определяемых пользователем как PRBS 7-, 23-, 31‑ и 40‑разрядные.

Блок DPMA содержит регистры конфигурации и связан по JTAG для периферийного сканирования.

Блок-схема SerDes и отдельно блок-схема приемника показаны на рис. 12 и 13 соответственно.

Канал связи между сериализатором и десериализатором можно представить как четырехполюсник, значительно ослабляющий высокие частоты, примерно так, как показано на рис. 14. Для того чтобы скомпенсировать ослабление высокой частоты в канале, необходимо поднять усиление тракта передачи и приема по высокой частоте. Для этого в тракт передачи вводят предыскажения по высокой частоте, а в тракт приема вводят эквалайзеры.

На рис. 15 показан типичный канал передачи данных: сериализатор – канал – эквалайзер – блок восстановления данных и синхрочастоты – десериализатор. На рис. 16 показана частотная коррекция тракта приема по высокой частоте. Однако обычные линейные цепи частотной коррекции по высокой частоте не могут дать большого усиления из-за того, что они «забиваются» высокочастотными шумами и импульсными помехами. Поэтому в канале приема применен эквалайзер подстройки по обратной связи, блок-схема которого приведена на рис. 17. На рис. 18 показаны импульсы на выходе передатчика, причем на передних фронтах импульсов видны предыскажения по высокой частоте. На рис. 19а показаны эти же импульсы после прохождения линии связи, а на рис. 19б — на выходе эквалайзера.

Рис. 15. Канал передачи данных: сериализатор – канал – эквалайзер – блок восстановления данных и синхрочастоты – десериализатор

Рис. 19. Импульсы после прохождения линии связи и на выходе эквалайзера:

а) принимаемые данные;

б) принимаемые данные после эквалайзера

Блок подуровня физического кодирования

Блок PCS (Physical Coding Sublayer) имеет модульную архитектуру с возможностью функции обхода некоторых частей этого блока. В блоке PCS выполняется кодирование 8b/10b и 128b/130b, а также выравнивание символов, инверсия полярности, реверс битов. Для компенсации параметров разных синхроимпульсов с различными фазами этих импульсов имеется встроенное FIFO. Линии могут объединяться в группы, между линиями производится выравнивание задержек. Блок PCS имеет низкие и детерминированные режимы латентности для таких протоколов, как CPRI и OBSAI.

Программируемый интерфейс применяется для контроля состояния и динамического конфигурирования работы SerDes. Также для тестирования и отладки может быть программно установлено до семи различных режимов «заглушки» на ближнем или на дальнем конце в PMA и PCS.

Для проведения тестирования имеется встроенный тест самопроверки (BIST):

- в PCS генерируются и проверяются паттерны, определяемые пользователем как PRBS 7-, 15-, 23-, 31- и 40‑разрядные;

- в PMA генерируются и проверяются паттерны, определяемые пользователем как PRBS 7-, 23-, 31- и 40‑разрядные.

Кроме того, для проведения тестирования и отладки имеется встроенный блок осциллографирования, позволяющий снимать глазковую диаграмму для канала Rx. Диаграмма позволяет выполнять измерения как по времени, так и по амплитуде.

Блоки PCS в передатчике (Tx)

В этом разделе приводится описание канала передачи данных (Tx) в PCS. В канале передачи данных блок PCS получает информацию от ядра логики и передает ее на уровень PMA. Сведения могут подаваться как на кодер, так и в обход кодера.

Основными составными частями блока канала передачи являются кодер передатчика и блок изменения полярности битов (PBR). Кодер кодирует данные для линии передачи. Его основная задача состоит в том, чтобы гарантированно поддерживать баланс линии передачи по постоянному току. Для этого кодер устраняет длинные последовательности единиц или нулей. Блок PBR производит инверсию полярности данных и перестановку данных, которые будут переданы в канале передачи.

Простейший вариант конфигурации блока IP SerDes — это одна линия. Упрощенная блок-схема информационного канала передачи Tx приведена на рис. 20. Здесь представлена одна линия передачи. Причем SerDes сконфигурирован в универсальном режиме и поддерживает кодирование только по 8b/10b. Может использоваться лишь один PBR#0 или PBR#1, или они оба включены в обход. Блок PCS можно сконфигурировать таким образом, что несколько линий объединены в один канал приема/передачи данных для SerDes. Максимальное число линий — 12.

Перечень поддерживаемых стандартов, в которых может работать PCS, приведен в таблице 6.

|

Наименование интерфейса |

Число линий |

Гбит/с на линию |

PCS |

PMA |

||||||

|

Разрядность внутренней шины на линию |

Кодирование |

Выравнивание слов |

Выравнивание линий |

Эллистичный буфер |

Spread Spectrum Clocking |

Режим Power-Down |

OOB Signaling |

|||

|

PCI Express 1.1 |

1/4/8 |

2,5 |

8/16 |

8b/10b |

K28,5 |

+ |

+ |

+ |

+ |

+ |

|

PCI Express 2.0 |

1/4/8 |

2,5/5 |

16 |

8b/10b |

K28,5 |

+ |

+ |

+ |

+ |

+ |

|

PCI Express 3.0 |

1/4/8 |

2,5/5/8 |

16 |

128b/130b |

K28,5 |

+ |

+ |

+ |

+ |

+ |

|

SRIO |

1/4/8 |

1,25/2,5/3,125/6,25 |

16 |

8b/10b |

K28,5 |

+ |

+ |

+ |

+ |

+ |

|

Gigabit Ethernet |

1 |

1,25 |

8 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

10 gigabit Ethernet (XAUI) |

4 |

3,125 |

8 |

8b/10b |

K28,5 |

+ |

+ |

|

|

|

|

10 gigabit Ethernet (XFI) |

1 |

10,3125 |

8 |

64b/66b |

Sync header |

|

|

|

|

|

|

40 gigabit Ethernet (XLAUI) |

4 |

10,3125 |

8 |

64b/66b |

Sync header |

|

|

|

|

|

|

100 gigabit Ethernet (CAUI) |

10 |

10,3125 |

8 |

64b/66b |

Sync header |

|

|

|

|

|

|

SGMII |

1 |

1,25 |

8 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

Fibre Channel-1 |

1 |

1,065 |

8 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

Fibre Channel-2 |

1 |

2,125 |

8 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

Fibre Channel-4 |

1 |

4,25 |

16 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

Fibre Channel-8 |

1 |

8,5 |

16 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

Fibre Channel-10 |

1 |

10,52 |

16 |

8b/10b |

K28,5 |

|

+ |

|

|

|

|

SATA Gen 1 |

1 |

1,5 |

10 |

8b/10b |

K28,5 |

|

|

+ |

+ |

+ |

|

SATA Gen 2 |

1 |

3 |

10 |

8b/10b |

K28,5 |

|

|

+ |

+ |

+ |

|

SATA Gen 3 |

1 |

6 |

10 |

8b/10b |

K28,5 |

|

|

+ |

+ |

+ |

|

SAS |

1 |

1,5/3/6 |

10 |

8b/10b |

K28,5 |

|

|

+ |

+ |

|

|

Interlaken |

6, 8, 10, 12, 24 |

4, 6–12, 74 |

20 |

64b/67b |

Sync header |

(2) |

|

|

|

|

|

CEI6-SR |

1 |

4,976–6,375 |

16 |

|

|

|

|

|

|

|

|

CEI6-LR |

1 |

4,976–6,375 |

16 |

|

|

|

|

|

|

|

|

CEI11-SR |

1 |

9,95–11,1 |

16 |

|

|

|

|

|

|

|

|

SPI-5 |

19 |

3,125 |

8 |

|

(2) |

(2) |

|

|

|

|

|

SFI-5.1 (3) |

19 |

2,488–3,125 |

8 |

|

(2) |

(2) |

|

|

|

|

|

SFI-5.2 (3) |

19 |

9,95–11,1 |

8 |

|

(2) |

(2) |

|

|

|

|

|

SFI-5.3 (3) |

19 |

9,95–11,1 |

8 |

|

(2) |

(2) |

|

|

|

|

|

Infiniband |

1 |

2,5/5/10 |

8 |

|

(2) |

(2) |

|

|

|

|

|

OC48 (1) |

1 |

2,488 |

8 |

|

(2) |

|

|

|

|

|

|

GPON |

1 |

1,25/5/10 |

8 |

|

(2) |

|

|

|

|

|

|

EPON |

1 |

1,25/5/10 |

8 |

|

(2) |

|

|

|

|

|

|

CPRI |

1 |

1,228/2,456/ |

|

|

|

|

|

|

|

|

|

3,072/6,144 |

8 |

|

(2) |

|

|

|

|

|

|

|

|

OBSAI |

1 |

1,228/2,456/ |

|

|

|

|

|

|

|

|

|

3,072/6,144 |

8 |

|

(2) |

|

|

|

|

|

|

|

|

Backplane interconnect (with DFE) |

1–20 |

1,25–12,74 |

8/16 |

|

|

|

|

|

|

|

Примечания.

(1) — не поддерживается в аппаратно интегрированном блоке PCS (необходимо устанавливать в логике).

(2) — опционально.

(3) — сдвигатель битов (Bit slider) работает в протоколе SFI.

Кодеры канала передачи

Каждый кодер получает данные, поступающие на вход PCS, и на выходе генерирует свое закодированное слово данных. Кодеры могут работать с 1‑байтовыми данными или данными, имеющими разрядность двойного слова в 16 битов, при этом для обработки 16‑битовых данных кодеры включаются каскадно. Вывод кодера подсоединяют к PMA для передачи данных в выходной сериализатор.

Кодер 8b/10b обеспечен дополнительной логикой, полностью поддерживающей протоколы гигабитный Ethernet, XAUI и PCIe (gen1, gen2).

Кодер 64b/66b имеет дополнительную логику, которая полностью поддерживает протоколы: Ethernet 10/40/100 Гбит/с и другие протоколы со скоростями передачи данных более 10 Гбит/с.

Кодер 64b/67b поддерживает Interlaken.

Кодер 128b/130b специально сделан для поддержки протокола PCIe gen3. Функция совместима со спецификацией PCIe, работающего в режиме конвейера, и взаимодействует со встроенным IP-ядром PCIe для поддержки gen3.

Другие протоколы, требующие универсального кодера 8b/10b или 128b/130b, могут также использовать этот функциональный блок.

Канал приема

В канале приема PCS получает данные от PMA и передает их в интерфейс, связывающий его с ядром логики. Блок-схема канала приема PCS показана на рис. 21. Десериализатор, работающий на уровне принятых байтов, может быть реализован в интерфейсе, связывающем его с ядром логики, это позволяет ослабить требования к синхро-частоте.

Канал приема состоит из следующих частей:

- блок логики выбора фазы;

- блок изменения полярности и разрядного инвертирования;

- блок выравнивания символов;

- блочная синхронизация и декодирование по 128b/130b;

- блок выравнивания задержек сигналов между линиями (до 12 каналов);

- блок компенсации синхрочастоты;

- декодер 8b/10b;

- блок проверки правильности числа переходов;

- побитовый сдвигатель;

- блок сдвига принятого бита позволяет исправлять или задерживать данные на один период синхрочастоты в дополнение к общему сдвигу в один период синхрочастоты.

Логика выбора фазы

Блок выбора фазы (PPL, Phase picking logic) предназначается для использования в режиме работы передискретизации CDR в PMA. Блок PPL принимает передискретизированные данные от PMA и реализует алгоритм для извлечения полученных битов данных. Блок PPL также обеспечивает обратную связь на уровне фазового перехода к PMA. Это нужно для того, чтобы учесть любое смещение частоты между принимаемыми данными на линии и синхрочастотой передискретизации. Для работы в режиме передискретизации поддерживаются следующие конфигурации:

- 4×-передискретизация, до 6,25 Гбит/с;

- 8×-передискретизация, до 3,125 Гбит/с.

Блок изменения полярности и инвертирования бита

В канале приема есть два независимых блока, в которых можно произвести настройку для изменения полярности и поразрядного инвертирования данных (PBR, Polarity Bit Reversal). Предусмотрена также опция, позволяющая динамически инвертировать данные, поступающие от PMA на Rx. Блок инвертирования бита используется для того, чтобы инвертировать биты данных, менять местами байты (swap byte ordering) и менять местами биты (reverse bit-ordering). В тракте приема имеется два блока PCS, что также соответствует двум блокам PCS в тракте передачи.

Когда производится изменение полярности при передаче бита в тракте передачи, перед тем как данные будут закодированы в соответствии с протоколом передачи, то в тракте передачи используется PBR #0 (рис. 20) и, соответственно, в тракте приема применяется блок PBR #0 (рис. 21). Напротив, если операция PBR выполняется на самом выходе в тракте передачи на уже закодированных данных, то используется блок PBR #1 (рис. 20) и, соответственно, в тракте приема — PBR #1 (рис. 21), в котором выполняется изменение полярности бита, прежде чем будет произведено выравнивание и декодировка символа. Как отмечено ранее, оба блока могут быть отключены и в тракте передачи, и в тракте приема.

Блок выравнивания символов

Параллельный вывод данных от сериализаторов PMA должен быть выровнен к границам байта, прежде чем эти данные могут использоваться принимающей логикой. Сторона передачи обычно отправляет специальные разделительные символы, которые применяются для выравнивания. Также в качестве разделителей используются и последовательности символов. Атрибуты для выравнивания и последовательности обнаружения символов определяются по 10‑разрядным данным. Но если приемный информационный канал находится в 8‑разрядном (или 16‑разрядном) режиме, то рассматриваются только младшие восемь битов атрибута.

Блок выравнивания символов может быть сконфигурирован таким образом, чтобы поддерживать множество стандартов (табл. 6).

Блок выравнивания символа ищет эти символы и устанавливает границу байта, а также поддерживает выравнивание для двух различных символов и может обнаружить соответствие последовательности с четырьмя символами.

Режимы работы

Можно программно задать следующие режимы работы блока выравнивания символов:

- Ручной режим — производится выравнивание к заранее заданному символу для каждого запроса от ядра логики.

- Режим сдвига битов — выполняется сдвиг бита на 1 разряд из данных для каждого запроса от ядра логики.

- Автоматический режим — в этом режиме работает конфигурируемый конечный автомат, который автоматически производит выравнивание к заранее заданному символу. Чтобы определить потерю выравнивания, в счетчик ошибок автомата введен заранее задаваемый гистерезис на число ошибок.

Ручной режим

В ручном режиме выравнивания принятых символов блок выравнивания пытается определить, соответствует ли поток данных, поступающий от выхода PMA десериализатора или от блока выбора фазы, предварительно заданному образцу, и если это соответствие найдено, то происходит захват. Операция выравнивания управляется пользовательской логикой в ядре ПЛИС на положительном фронте RX_com_det_en. Блок выравнивания символа ищет соответствие получаемых данных с предварительно заданным образцом для выравнивания. Ядро ПЛИС при этом будет ожидать состояния захвата, и как только во входящем потоке битов происходит захват положения границы слова, то логика в ядре ПЛИС может контролировать ошибочное состояние от декодера 8b/10b или использовать любой другой механизм в ядре ПЛИС, чтобы идентифицировать потерю захвата. Далее ядро ПЛИС выдает следующий положительный фронт, чтобы вызвать новый цикл выравнивания.

Режим сдвига битов

В режиме сдвига битов выравниванием символов управляет логика пользователя, делается это с помощью сигнала RX_bit_slip_en. Каждый положительный фронт RX_bit_slip_en заставляет логику выравнивания символов перемещать границу слова на один бит, и блок выравнивания символа пытается определить, соответствует ли полученный символ в пределах новой границы слова заданному образцу символа для выравнивания. Если граница слова не найдена, логика пользователя может снова установить RX_bit_slip_en, возможно после ожидания окончания процесса сдвига, при котором граница слова переместится на другой бит в принятых данных. Этот цикл продолжается до тех пор, пока не находится символ и не происходит захват положения границы слова. Как только во входящем потоке битов происходит захват положения границы слова, то логика в ядре ПЛИС может контролировать ошибочное состояние от декодера 8b/10b или применить любой другой механизм в ядре ПЛИС, чтобы идентифицировать потерю захвата. Режим сдвига битов поддерживает все атрибуты, используемые для ручного режима выравнивания. Максимальное количество сдвигов, которые вызовут истинное изменение в выравнивании, ограничивается разрядностью информационного канала.

Автоматический режим

В автоматическом режиме выравнивания блок выравнивания автоматически определяет границы слова, используя для этого предварительно заданные символы — разделители, обозначающие границы слова. Также блок может определить потерю условия захвата символов выравнивания. Для этого в него предварительно задается количество плохих кодовых комбинаций (или символов выравнивания на различной границе слов). Символы разделителей применяются для того, чтобы идентифицировать корректную границу символа. Поэтому на приемном конце входящие данные сканируются для поиска символов разделителей. Как только символ разделителя находится, десериализатор устанавливает границу слова полученных данных. Полученные данные непрерывно сканируются для поиска последующих символов разделителей.

Выравнивание задержек в линиях

Блок PCS имеет возможность реализовать выравнивание задержек в линиях при прохождении данных через сериализаторы на одной стороне микросхемы (до 12 линий). Но выравнивание задержек в линиях на различных сторонах микросхемы не производится. Функция выравнивания поддерживает до двух различных образцов задержек (до пяти символов длины в каждом из образцов). Функция выравнивания задержек имеет следующие режимы:

- Автоматическое выравнивание задержек в линиях.

- Ручное выравнивание задержек в линиях.

- Пропуск символа. Данные в этой линии «проталкиваются вперед» или задерживаются (advanced or delayed) на 1–2 такта.

Компенсация синхрочастоты

Приемные данные от PMA синхронизированы к восстановленной синхрочастоте, которая выводится из CDR (кроме режима передискретизации CDR). Для некоторых протоколов требуется, чтобы данные были синхронизированы с внутренней системной синхрочастотой SerDes на 12,75 Гбит/с (обычно это синхрочастота передачи). Функция компенсации синхрочастоты использует эластичный буфер, чтобы компенсировать любое смещение частоты между восстановленной синхрочастотой и внутренней системной синхрочастотой. Эта функция используется в приемном потоке данных для компенсации любого смещения частоты, производится заранее установленное число пропусков символов или заполнения символами.

Декодер 8b/10b

Декодер 8b/10b генерирует 8‑разрядные слова кода данных и 1‑битные сигналы управления из 10‑разрядных входных закодированных данных. Он использует групповое декодирование в соответствии с IEEE 802.3 п. 36. Если применяется 16‑разрядный информационный канал, то два декодера 8b/10b включаются каскадно для получения 16‑разрядных данных для ядра ПЛИС.

Декодер 128b/130b

Блок декодирования 128b/130b поддерживает протокол PCIe Gen3. Он совместим со спецификацией PIPE.

Сдвигатель бит

Сдвигатель бит — это 80‑разрядное циклическое сдвиговое устройство, которое может использоваться для того, чтобы управлять побитовым выравниванием данных, поступающих от ядра ПЛИС. Эта функция предназначена для того, чтобы реализовать любой алгоритм, необходимый пользователю для выравнивания данных на битовом уровне или для выравнивания задержек в линиях. Он может применяться в соединении с режимом сдвига символа в функции выравнивания задержек, чтобы достигнуть широкого диапазона по выравниванию задержек.

Блок проверки правильности числа переходов (TDC — Transition Density Checker)

Блок проверки правильности числа переходов, или плотности переходов, контролирует параллельную шину данных RX от PMA и число последовательных нулей или единиц. Если это число достигает предварительно заданного значения порога, то блок проверки устанавливает бит триггера так, чтобы указать на нарушение плотности переходов. Это предварительно заданное значение определяет порог для нахождения ошибки, минимальный запрограммированный порог равен половине разрядности информационного канала. В случае если используется масштабирование, фактический эффективный порог будет равен:

ЭГ = (ПГ×М)+0,5 Р;

где ЭГ — эффективный гистерезис; ПГ — запрограммированный гистерезис; М — масштабирование; Р — разрядность данных.

Сигнал от блока проверки плотности переходов может быть передан в ядро ПЛИС в логику пользователя. При работе с блоком проверки плотности переходов необходимо учитывать, что любой переход бита может вызвать переполнение счетчика и его очистку, а затем он может снова начать считать.

Интерфейс управления

У блоков PCS и PMA есть параллельная шина интерфейса управления, которая разрешает пользовательской логике конфигурировать информационный канал и также контролировать состояние основных блоков. Интерфейс управления реализуется как набор сигналов: протокол запроса и подтверждения доступа к шине, 8‑разрядные данные, сигнал чтения шины, сигнал записи данных и 16‑разрядная шина адреса. Чтобы минимизировать использование выводов на стороне ядра ПЛИС, предоставляется и последовательная версия интерфейса управления. Последовательно-параллельные преобразователи реализуются в аппаратном ядре и соединяются с интерфейсом управления PMA и PCS. У каждой линии сериализаторов есть свой собственный интерфейс управления.

Заключение

Итак, мы ознакомились с третьей статьей, посвященной новым микросхемам семейства Speedster22i HD, работающим на максимальной частоте 750 МГц и имеющим 1,7 млн LUT. Они выполнены по 22‑нм техпроцессу на фабрике Intel и предназначены для Hi-End-устройств.

В этой части были более подробно рассмотрены программируемые порты ввода/вывода и сериализаторы.

В следующих статьях цикла мы продолжим рассматривать основную «изюминку» ПЛИС Speedster — аппаратные IP-ядра контроллеров интерфейсов, а также средства разработки и стартовые наборы.

- Руководство пользователя Speedster22i_SerDes_User_Guide_UG028.pdf.

- Таблица расположения выводов Speedster22iHD1000_Pin_Table.xlsx.

20 июня, 2022

20 июня, 2022 4 августа, 2020

4 августа, 2020 28 февраля, 2022

28 февраля, 2022