Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq 7000 AP SoC фирмы Xilinx.

Часть 11

Подключение применяемого загрузочного кабеля к соответствующему порту компьютера, на котором установлена САПР серии Xilinx ISE Design Suite, и разъему JTAG-интерфейса инструментального модуля, выбранного для реализации проектируемой микропроцессорной системы, целесообразно выполнять до активизации программных средств iMPACT.

Активизация средств конфигурирования ПЛИС и программирования микросхем Flash-памяти, представленных в составе САПР серии Xilinx ISE Design Suite

Для запуска средств конфигурирования ПЛИС и программирования микросхем Flash-памяти, входящих в состав САПР серии Xilinx ISE Design Suite, рекомендуется прежде всего в среде управляющей оболочки Project Navigator («Навигатора проекта») открыть созданный ранее проект аппаратной части разрабатываемой встраиваемой системы, процесс формирования которого был подробно рассмотрен в [11]. Далее необходимо выделить пункт Tools основного меню «Навигатора проекта», а затем в появившемся одноименном всплывающем меню выбрать команду iMPACT, как показано на рис. 1.

Рис. 1. Активизация средств конфигурирования ПЛИС и программирования микросхем Flash-памяти в САПР серии Xilinx ISE Design Suite

В процессе выполнения указанной команды в рабочей области основного окна управляющей оболочки САПР серии Xilinx ISE Design Suite отображается информационная панель с заголовком Warning, содержащая предупреждение об отсутствии сформированного проекта для средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. После закрытия информационной панели нажатием клавиши OK на экране разворачивается основное окно программного модуля iMPACT, чей вид представлен на рис. 2.

Рис. 2. Первоначальный вид основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти iMPACT

Первоначально открывшееся основное окно средств конфигурирования ПЛИС и программирования микросхем Flash-памяти САПР серии Xilinx ISE Design Suite не содержит никакой информации об используемом кристалле расширяемой процессорной платформы и загрузочном ППЗУ из-за отсутствия сформированного проекта. Для создания нового проекта необходимо выделить пункт File главного меню программного модуля iMPACT, а затем в открывшемся одноименном всплывающем меню выбрать строку New Project, как демонстрирует рис. 3. После этого на экран выводится диалоговая панель с заголовком Automatically create and save a project, которая предоставляет возможность выбора способа формирования нового проекта для средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. Рекомендуется воспользоваться автоматическим способом создания и сохранения нового проекта — процедуру можно выполнить нажатием клавиши Yes («Да»), расположенной в нижней части открывшейся диалоговой панели. При таком способе новый проект для программного модуля iMPACT формируется автоматически на основе информации, указанной при создании проекта аппаратной части разрабатываемой встраиваемой микропроцессорной системы в САПР серии Xilinx ISE Design Suite [11]. Если необходимо в ручном режиме создать новый проект для средств конфигурирования ПЛИС и программирования микросхем Flash-памяти, то в диалоговой панели Automatically create and save a project следует воспользоваться клавишей No («Нет»).

Рис. 3. Создание нового проекта средств конфигурирования ПЛИС и программирования микросхем Flash-памяти iMPACT

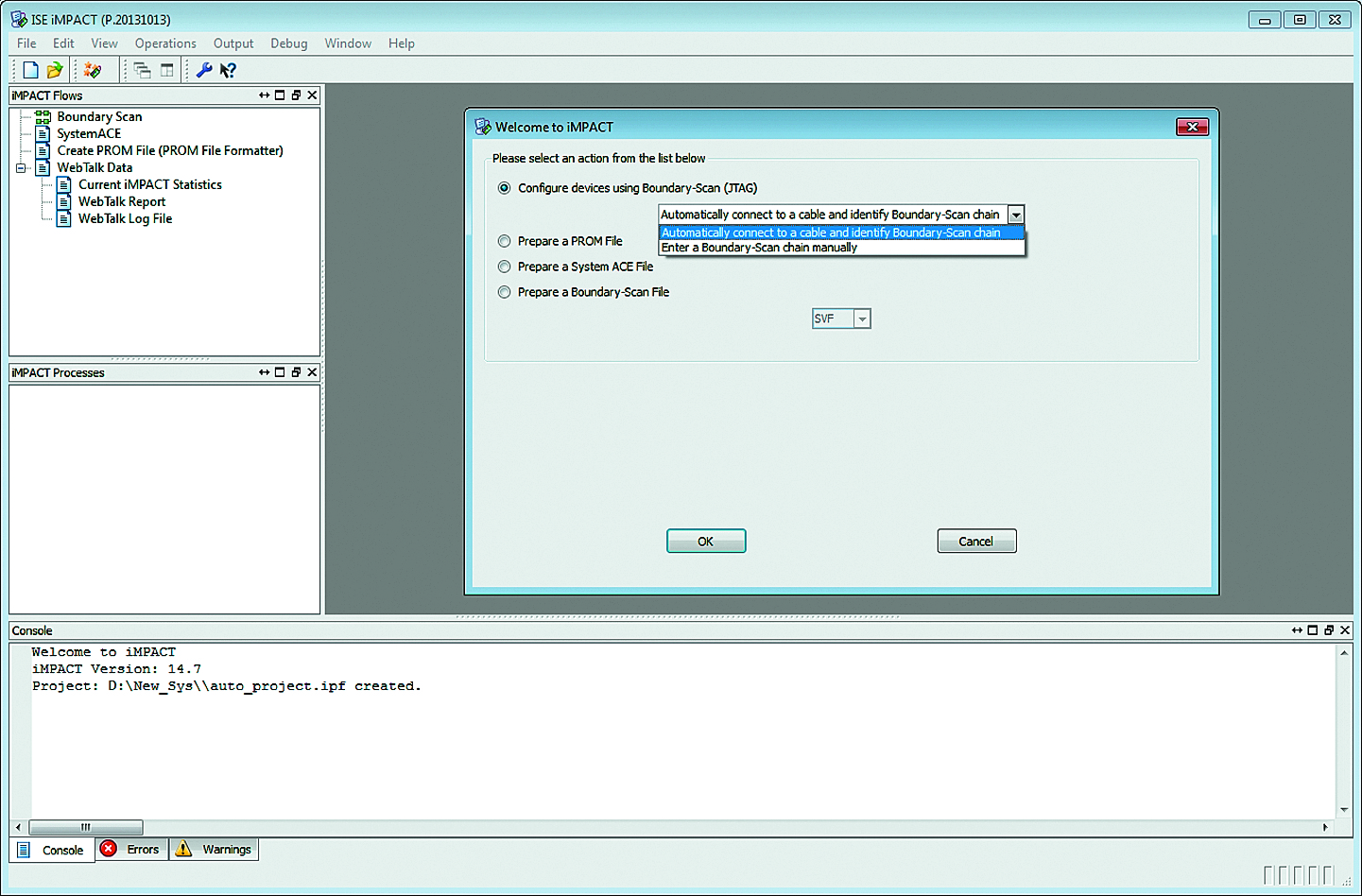

После выбора способа формирования нового проекта на экране появляется диалоговая панель с заголовком Welcome to iMPACT, чей вид приведен на рис. 4. Открывшаяся диалоговая панель предназначена для выбора необходимого режима функционирования программного модуля iMPACT.

Требуемый режим работы средств конфигурирования ПЛИС и программирования микросхем Flash-памяти устанавливается с помощью группы кнопок с зависимой фиксацией, представленных во встроенной панели Please select an action from the list below. При этом следует учитывать, что все выполняемые операции с микросхемами загрузочной Flash-памяти осуществляются в среде программного модуля iMPACT не напрямую, а через кристалл расширяемой процессорной платформы, для которого предназначено ППЗУ. Соответствующая конфигурационная информация для аппаратных ресурсов кристалла семейства Zynq‑7000 AP SoC автоматически загружается в режиме периферийного сканирования через порт JTAG-интерфейса при запуске требуемой операции. Поэтому для программирования микросхем загрузочной Flash-памяти и обратного чтения записанных данных нужно зафиксировать в нажатом состоянии кнопку Configure devices using Boundary-Scan (JTAG). Затем с помощью поля выбора, расположенного под этой кнопкой, надо указать режим обнаружения загрузочного кабеля и цепочки периферийного сканирования инструментального модуля, используемого для реализации разработанной микропроцессорной системы. В большинстве случаев рекомендуется установить режим автоматического обнаружения подключенного загрузочного кабеля и цепочки периферийного сканирования. Для этого в выпадающем списке указанного поля выбора следует выделить строку Automatically connect to а cable and identify Boundary-Scan chain. В некоторых ситуациях может понадобиться «ручной» способ определения состава цепочки периферийного сканирования. В частности, этот режим целесообразно использовать, когда в структуре применяемого инструментального модуля представлены не только кристаллы программируемой логики и расширяемых процессорных платформ фирмы Xilinx, но и ПЛИС других производителей. Для установки режима «ручного» определения цепочки периферийного сканирования в выпадающем списке следует выбрать вариант Enter a Boundary-Scan chain manually.

Если был установлен режим автоматической идентификации типа подключенного кабеля и цепочки периферийного сканирования, то далее средства конфигурирования ПЛИС и программирования микросхем Flash-памяти выполняют процедуру обнаружения загрузочного кабеля. Ход этого процесса отображается на экране дисплея с помощью всплывающей панели индикации и сопровождается соответствующей информацией во встроенной панели регистрации консольных сообщений Console, находящейся в нижней части основного окна программного модуля iMPACT, как демонстрирует рис. 5. Если не удается автоматически идентифицировать подключенный загрузочный кабель (например, из-за отсутствия напряжения питания), то на экран выводится информационная панель с заголовком Warning, содержащая соответствующее предупреждение. Аналогичное предупреждение отображается и во встроенной панели регистрации консольных сообщений Console.

В тех случаях, когда режим автоматического обнаружения не позволяет идентифицировать подключенный загрузочный кабель, можно указать его тип и основные параметры в «ручном» режиме. Для этого предназначена команда Cable Setup, представленная во всплывающем меню Output и контекстно-зависимом всплывающем меню, открываемом щелчком правой кнопки мыши при расположении курсора на вкладке Boundary Scan, которая автоматически добавляется в рабочей области основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. В процессе выполнения этой команды на экране появляется диалоговая панель с заголовком Cable Communication Setup, чей вид изображен на рис. 6.

В открывшейся диалоговой панели нужно в первую очередь указать тип применяемого загрузочного кабеля (соответственно вид интерфейса, используемого для коммутации с персональным компьютером) с помощью группы кнопок с зависимой фиксацией, расположенных во встроенной панели Communication Mode. При использовании загрузочных кабелей фирмы Xilinx JTAG Parallel Download Cable III и JTAG Parallel Download Cable IV, подключаемых к параллельному порту (LPT) персонального компьютера (ПК), необходимо зафиксировать в нажатом состоянии кнопку Parallel Cable III или Parallel Cable IV соответственно. В случае применения загрузочных кабелей фирмы Xilinx, подключаемых к универсальной последовательной шине USB ПК, Platform Cable USB и Platform Cable USB II в нажатое положение следует установить кнопку Platform Cable USB/II. Если для программирования загрузочного ППЗУ предполагается задействовать инструментальные средства загрузки, производимые компанией Digilent Incorporated, JTAG-USB Cable, JTAG HS1 Programming Cable for Xilinx FPGAs или JTAG-HS2 Programming Cable for Xilinx FPGAs, то в нажатое состояние нужно переключить кнопку Digilent USB JTAG Cable. Чтобы использовать для программирования микросхемы загрузочной Flash-памяти и чтения записанной информации выделенный аппаратный сервер, необходимо зафиксировать в нажатом положении кнопку HW Server.

После выбора типа загрузочного кабеля следует установить значения основных параметров его подключения. В поле выбора значения параметра Port указывается номер порта ПК, к которому подключен используемый кабель. В выпадающем списке возможных значений этого параметра представлены условные обозначения доступных портов компьютера, соответствующих типу применяемого загрузочного кабеля. Поле выбора значения параметра TCK Speed/Baud Rate предоставляет возможность установки требуемого варианта скорости передачи конфигурационных данных. Чтобы использовать значение скорости, установленное по умолчанию для выбранного типа загрузочного кабеля, в качестве значения этого параметра следует указать вариант Default Speed. Если необходимо задействовать значение скорости передачи конфигурационных данных, отличающееся от предлагаемого по умолчанию, то нужно в выпадающем списке допустимых значений поля выбора TCK Speed/Baud Rate выделить строку Select Speed.

Вариант подключения загрузочного кабеля к персональному компьютеру определяется с помощью двух кнопок с зависимой фиксацией — Local и Remote, представленных во встроенной панели Cable Location. Если кабель присоединен к локальному компьютеру, на котором развернуты средства конфигурирования ПЛИС и программирования микросхем Flash-памяти САПР серии Xilinx ISE Design Suite, то в нажатое состояние нужно переключить кнопку Local. При подсоединении загрузочного кабеля к компьютеру с удаленным доступом следует зафиксировать в нажатом положении кнопку Remote. В этом случае становится доступным поле редактирования значения параметра Host Name, где нужно с помощью клавиатуры указать имя компьютера с удаленным доступом, к которому присоединен загрузочный кабель, или его IP-адрес.

Диалоговая панель Cable Communication Setup предоставляет также возможность использовать предопределенную совокупность параметров подключения загрузочного кабеля. Для этой цели предусмотрены индикатор состояния параметра Open Cable Plug-in и поле выбора/редактирования значения параметра Select or enter a Plug-in from the list below, расположенные во встроенной панели Cable Plug-in. Чтобы воспользоваться предопределенным вариантом подключения инструментальных средств загрузки, нужно установить индикатор состояния параметра Open Cable Plug-in во включенное положение. При этом становится доступным поле выбора/редактирования значения параметра Select or enter a Plug-in from the list below, в котором нужно указать требуемый вариант предопределенной совокупности параметров подключения загрузочного кабеля.

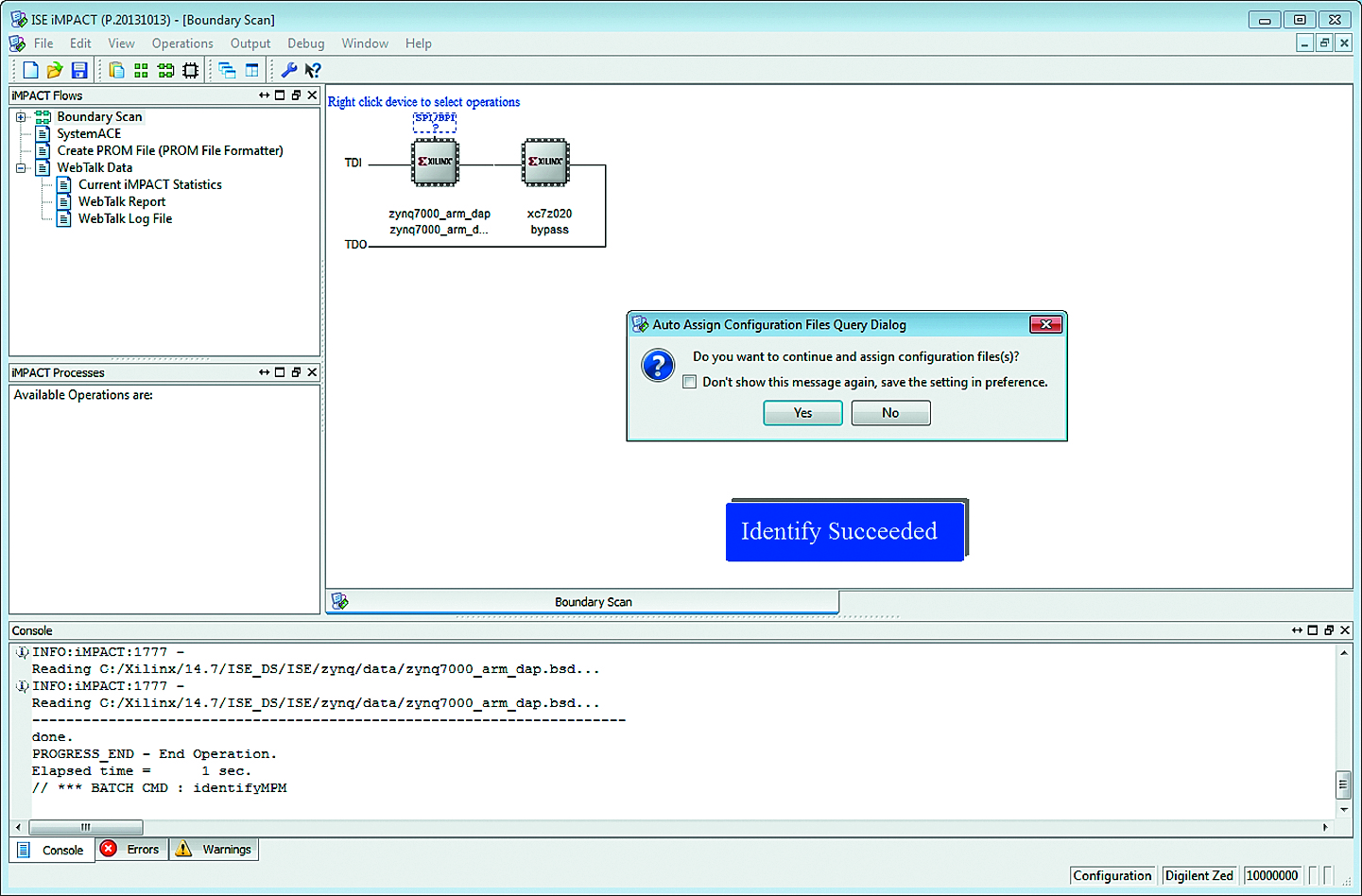

Процедура выбора типа загрузочного кабеля и параметров его подключения завершается нажатием клавиши OK, находящейся в нижней части диалоговой панели Cable Communication Setup (рис. 6). При успешной идентификации присоединенного загрузочного кабеля производится автоматический поиск и инициализация цепочки периферийного сканирования кристаллов программируемой логики и расширяемых процессорных систем, подключенной к выбранному JTAG-порту. Информация о составе идентифицированной цепочки периферийного сканирования отображается в графической форме на вкладке Boundary Scan рабочей области основного окна програм-много модуля iMPACT и в текстовом виде во встроенной панели регистрации консольных сообщений Console (рис. 7).

Следует обратить внимание на то, что каждый кристалл расширяемой вычислительной платформы представлен на указанной вкладке двумя условными графическими образами (УГО). Первый УГО соответствует процессорному блоку Processing System (PS) кристалла семейства Zynq‑7000 AP SoC, а второй — ресурсам программируемой логики Programmable Logic (PL). Под каждым условным графическим образом указывается тип представляемых ресурсов и название файла, содержащего соответствующую конфигурационную информацию. Условный графический образ микросхемы загрузочной Flash-памяти для кристалла расширяемой вычислительной платформы первоначально отображается на вкладке Boundary Scan в виде прямоугольного контура, выполненного штриховой линией, внутри которого указано обозначение SPI/BPI.

После определения состава идентифицированной цепочки периферийного сканирования инструментального модуля, применяемого для реализации разработанной встраиваемой микропроцессорной системы, на экран выводится диалоговая панель с заголовком Auto Assign Configuration Files Query Dialog, как показано на рис. 7. В открывшейся диалоговой панели есть запрос на выполнение процедуры назначения файлов, содержащих конфигурационную информацию для каждого элемента, представленного в составе цепочки периферийного сканирования. Учитывая, что для программирования микросхемы загрузочного Flash ППЗУ эта процедура не является необходимой, рекомендуется отрицательно ответить на приведенный запрос, нажав клавишу No («Нет»), находящуюся в нижней части диалоговой панели Auto Assign Configuration Files Query Dialog. После закрытия этой панели на экране появляется очередная диалоговая панель с заголовком Device Programming Properties, чей вид представлен на рис. 8.

Рис. 8. Определение параметров программирования элементов, представленных в составе цепочки периферийного сканирования

Данная диалоговая панель предоставляет возможность поочередного определения параметров программирования для каждого элемента, имеющегося в составе идентифицированной цепочки периферийного сканирования. При осуществлении операций записи и чтения данных из Flash ППЗУ можно воспользоваться значениями, установленными по умолчанию для этих параметров, подтвердив их нажатием клавиши OK, представленной в нижней части диалоговой панели Device Programming Properties.

Для выполнения операций программирования микросхемы загрузочной Flash-памяти и последующего чтения информационных и контрольных данных необходимо расположить курсор на контурном изображении ее УГО (SPI/BPI) и щелкнуть правой кнопкой мыши. Затем в открывшемся всплывающем меню нужно воспользоваться командой Add SPI/BPI Flash, как демонстрирует рис. 9. При выполнении этой команды на экране появляется диалоговая панель с заголовком Add PROM File, которая позволяет указать файл программирования для выбранной микросхемы загрузочного Flash ППЗУ.

В открывшейся диалоговой панели следует найти раздел, где был записан сгенерированный файл прошивки микросхемы Flash-памяти, содержащий загрузочный образ для разработанной микропроцессорной системы, как показано на рис. 9. В этом разделе нужно выбрать идентификатор требуемого файла программирования для загрузочного Flash ППЗУ, имеющий расширение mcs. Процесс формирования файла «прошивки» микросхемы загрузочной Flash-памяти проектируемой встраиваемой системы, реализуемой на базе кристалла расширяемой вычислительной платформы семейства Zynq‑7000 AP SoC, был подробно рассмотрен в [27]. Выбранный идентификатор файла прошивки микросхемы Flash-памяти, используемой для загрузки конфигурации аппаратной части и программного обеспечения разработанной микропроцессорной системы, надо подтвердить нажатием клавиши Open («Открыть»), расположенной в нижней части диалоговой панели Add PROM File. После этого на экран выводится следующая диалоговая панель, имеющая заголовок Select Attached SPI/BPI, чей вид приведен на рис. 10.

Рис. 10. Выбор типа микросхемы загрузочной Flash-памяти и определение параметров обратного чтения записанной информации

В этой диалоговой панели необходимо указать тип применяемой микросхемы загрузочной Flash-памяти, а также определить значения основных параметров обратного чтения информации, записанной в ППЗУ. Тип микросхемы Flash-памяти, предназначенной для записи загрузочного образа проектируемой микропроцессорной системы, определяется с помощью поля выбора значения параметра Select the PROM attached to FPGA. Выпадающий список возможных значений этого параметра включает два варианта — QSPI и NOR, которые соответствуют микросхемам ППЗУ типов Quad-SPI Flash и NOR Flash. После выбора требуемого варианта значения параметра Select the PROM attached to FPGA, соответствующего типу Flash-памяти, представленной в составе инструментального модуля, предназначенного для реализации разрабатываемой встраиваемой системы, нужно указать режим подключения микросхем ППЗУ к кристаллу расширяемой вычислительной платформы. Требуемый режим подключения микросхемы Flash-памяти к кристаллу семейства Zynq‑7000 AP SoC определяется с помощью второго поля выбора (рис. 10). В частности, для программирования загрузочного ППЗУ микропроцессорной системы, реализуемой на базе отладочной платы ZedBoard, в перечисленных полях выбора надо указать варианты QSPI и Single соответственно.

В случае необходимости выполнения операции чтения записанных информационных данных из микросхемы загрузочной Flash-памяти и сохранения их в виде файла на диске компьютера нужно определить значения основных параметров этого процесса. Для установки требуемых значений указанных параметров следует прежде всего переключить индикатор состояния параметра Readback to file Options в положение «Включено». После чего становятся доступными поля редактирования значений параметров Start Address (Hex) и Number of Bytes. Параметр Start Address (Hex) определяет значение стартового адреса, начиная с которого будут считываться данные, записанные в Flash ППЗУ. Значение начального адреса указывается с помощью клавиатуры в соответствующем поле редактирования в шестнадцатеричном формате. Значение параметра Number of Bytes определяет количество байт считываемых данных. Все установленные значения параметров вступают в силу при нажатии клавиши OK, находящейся в нижней части диалоговой панели Select Attached SPI/BPI. После закрытия указанной диалоговой панели контурное изображение УГО микросхемы Flash-памяти, представленное на вкладке Boundary Scan, автоматически заменяется полноценным условным графическим образом (рис. 11).

Для выполнения операций записи загрузочного образа разработанной микропроцессорной системы в Flash ППЗУ, а также для обратного чтения записанных данных и контрольной информации необходимо в первую очередь выделить УГО микросхемы Flash-памяти, поместив на него курсор и щелкнув левой кнопкой мыши. При этом во встроенной панели iMPACT Processes основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти САПР серии Xilinx ISE Design Suite появится интерактивный список операций, доступных для выбранной микросхемы ППЗУ. Для выполнения требуемой операции следует расположить курсор на соответствующей строке этого списка и дважды щелкнуть левой кнопкой мыши. Кроме того, активизация необходимой операции может осуществляться с помощью одноименных команд, представленных во всплывающем меню Operations и контекстно-зависимом всплывающем меню (рис. 11). Последнее меню вызывается щелчком правой кнопки мыши при расположении курсора на условном графическом образе микросхемы Flash ППЗУ.

Программирование микросхемы загрузочной Flash-памяти в среде САПР серии Xilinx ISE Design Suite

Запись конфигурационной последовательности аппаратной части проектируемой микропроцессорной системы и разработанного программного обеспечения в микросхему загрузочной Flash-памяти, чей условный графический образ выделен на вкладке Boundary Scan, выполняется командой Program. В процессе исполнения команды Program производится копирование загрузочного образа разработанной встраиваемой системы из файла, указанного в диалоговой панели Add PROM File (рис. 9), в выбранную микросхему Flash ППЗУ. Краткие сведения о ходе выполнения этого процесса отображаются в наглядном виде в информационной панели Configuration Operation Status, чей вид представлен на рис. 11. Более подробные сообщения обо всех шагах программирования микросхемы загрузочной Flash-памяти выводятся в консольной области основного окна программного модуля iMPACT.

Длительность процесса программирования микросхемы загрузочной Flash-памяти зависит от объема записываемых данных и может достигать нескольких минут. В случае успешного завершения записи загрузочного образа разработанной микропроцессорной системы в ППЗУ в рабочей области основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти появляется всплывающая панель, содержащая сообщение Program Succeeded (рис. 12). Соответствующее сообщение с указанием длительности процесса программирования микросхемы загрузочного Flash ППЗУ отображается также в консольной области основного окна программного модуля iMPACT.

Рис. 12. Отображение информации об успешном завершении процесса программирования микросхемы загрузочной Flash-памяти

В ряде случаев в текущем сеансе работы средств конфигурирования ПЛИС и программирования микросхем Flash-памяти может возникнуть необходимость повторной записи загрузочной информации в ППЗУ, но уже из другого файла прошивки. Перепрограммирование микросхемы загрузочной Flash-памяти может потребоваться, например, для исследования функционирования разработанной встраиваемой микропроцессорной системы с использованием различных версий конфигурации аппаратной части и программного обеспечения. Чтобы назначить другой файл прошивки для загрузочного ППЗУ, нужно воспользоваться командой Assign Configuration File из всплывающего меню Edit (рис. 13). При выполнении этой команды открывается диалоговая панель с заголовком Add PROM File, которая предоставляет возможность выбора нового варианта файла программирования для микросхемы загрузочной Flash-памяти. После определения требуемой версии файла загрузочного образа можно повторно воспользоваться командой программирования Flash ППЗУ, рассмотренной выше.

Для получения информации о текущем используемом файле прошивки загрузочного ППЗУ достаточно поместить указатель мыши на соответствующий условный графический образ, представленный на вкладке Boundary Scan основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. После этого в рабочей области отображается всплывающая панель, чей вид представлен на рис. 14.

В открывшейся всплывающей панели содержатся сведения о текущем файле программирования микросхемы Flash-памяти с указанием полного пути доступа к нему. Кроме того, в этой же панели приводится информация о типе используемой микросхемы Flash ППЗУ.

Верификация информации, содержащейся в загрузочном Flash ППЗУ

Для контроля соответствия загрузочного образа разработанной микропроцессорной системы, представленного в Flash ППЗУ и содержащегося в исходном файле прошивки, предусмотрена команда Verify. В процессе такого контроля выполняется чтение данных из запрограммированной микросхемы Flash-памяти и сравнение их с содержимым файла прошивки, который был назначен для соответствующего условного графического образа, представленного на вкладке Boundary Scan. Информация о результатах верификации выводится в рабочей области основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти и встроенной панели регистрации консольных сообщений Console. Если данные, записанные в загрузочном ППЗУ, совпадают с содержимым указанного файла прошивки, то в рабочей области основного окна программного модуля iMPACT появляется всплывающая панель с сообщением Verify Succeeded, как демонстрирует рис. 15. В противном случае отображается всплывающая панель, содержащая сообщение Verify Failed.

Контроль достоверности информации, имеющейся в запрограммированной микросхеме Flash-памяти, может осуществляться и с помощью контрольной суммы. Для подсчета контрольной суммы данных, представленных в загрузочном ППЗУ, предназначена команда Get Device Checksum. При успешном завершении процесса вычисления значения контрольной суммы в рабочей области основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти появляется всплывающая панель с сообщением Checksum Succeeded (рис. 16).

Результат суммирования данных загрузочного ППЗУ, полученный при выполнении команды Get Device Checksum, сравнивается со значением контрольной суммы файла прошивки, который был указан для соответствующего условного графического образа, выделенного на вкладке Boundary Scan основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. При совпадении этих значений в консольной области основного окна програм-много модуля iMPACT появляется сообщение Calculated checksum matches expected checksum, сопровождаемое значением контрольной суммы. В противном случае отображается сообщение The Calculated checksum differs from the expected checksum с указанием ожидаемого и полученного значений контрольной суммы.

Чтение загрузочной информации, содержащейся в запрограммированной микросхеме Flash-памяти

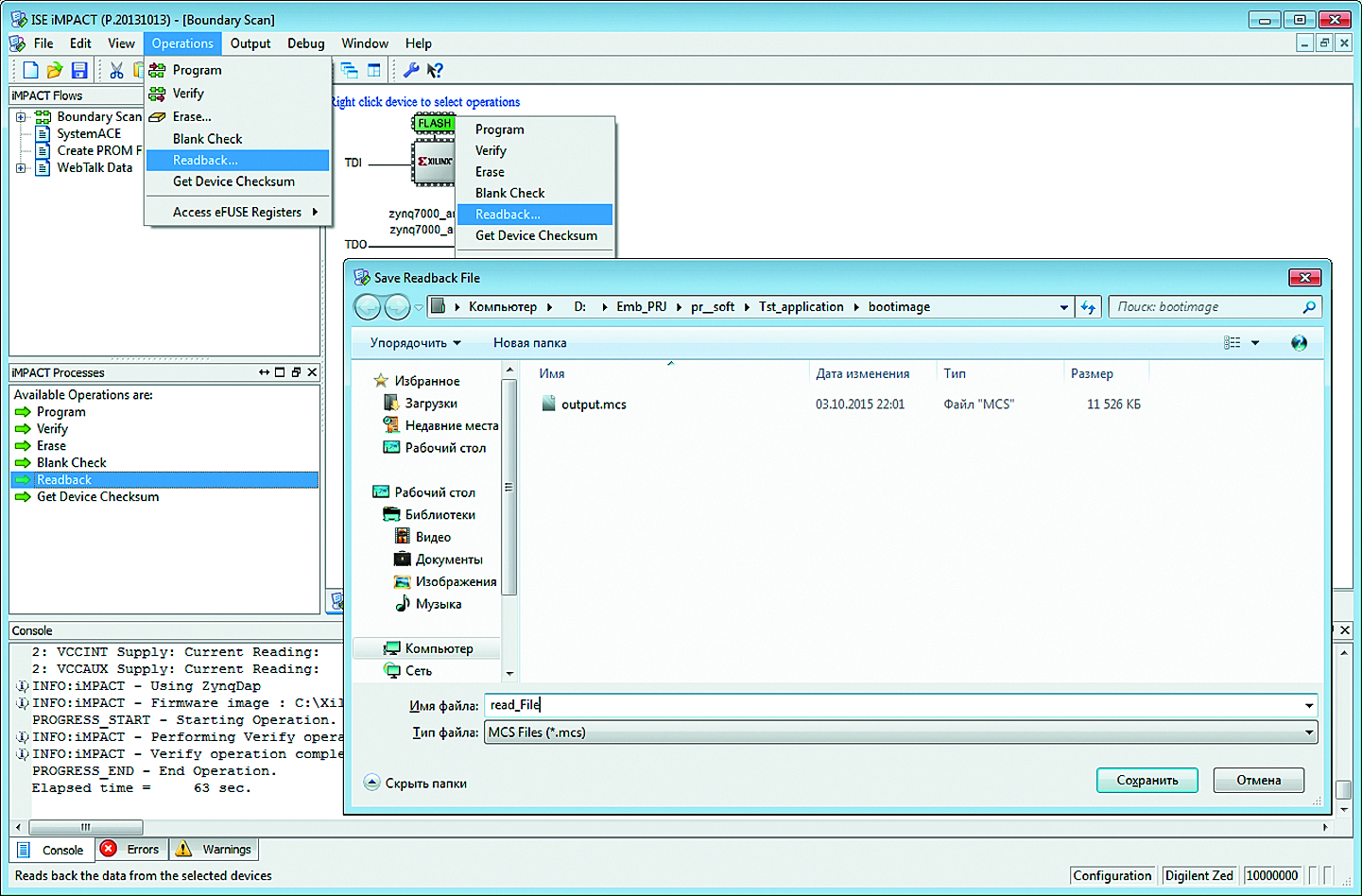

Для чтения загрузочной информации, содержащейся в запрограммированной микросхеме Flash-памяти, предназначена команда Readback. Считанный загрузочный образ разработанной встраиваемой микропроцессорной системы сохраняется в виде файла на диске в формате MCS, который может использоваться впоследствии для программирования других микросхем ППЗУ. Выполнение команды Readback начинается с вывода диалоговой панели с заголовком Save Readback File, в которой необходимо указать идентификатор создаваемого файла и выбрать место его сохранения на диске (рис. 17).

Рис. 17. Запуск процесса считывания данных из запрограммированной микросхемы загрузочной Flash-памяти

Выбрав требуемый раздел и определив название создаваемого файла, нужно подтвердить их нажатием клавиши Save («Сохранить»), представленной в нижней части этой диалоговой панели. Сразу после закрытия диалоговой панели Save Readback File начинается процесс чтения данных из загрузочного ППЗУ. Дальнейший ход этого процесса отображается с помощью соответствующей всплывающей панели индикации, которая появляется в рабочей области основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. При успешном окончании рассматриваемого процесса на экран выводится всплывающая панель, содержащая сообщение Readback To File Succeeded, как показано на рис. 18. Соответствующая информация появляется также во встроенной панели регистрации консольных сообщений Console основного окна программного модуля iMPACT.

Рис. 18. Отображение информации о выполнении процесса чтения данных из запрограммированной микросхемы загрузочной Flash-памяти

Удаление загрузочной информации из запрограммированной микросхемы Flash-памяти

Для получения информации о состоянии микросхемы загрузочной Flash-памяти (запрограммирована она или нет) следует использовать команду Blank Check. Сведения о статусе загрузочного ППЗУ, полученные при выполнении этой команды, приводятся во всплывающей панели, отображаемой в рабочей области основного окна средств конфигурирования ПЛИС и программирования микросхем Flash-памяти. Если микросхема загрузочной Flash-памяти находится в незапрограммированном состоянии, то в этой панели представлено сообщение Part is Blank. При наличии записанных данных в загрузочном ППЗУ во всплывающей панели отображается сообщение Part is not Blank, как демонстрирует рис. 19. Соответствующие сообщения выводятся также во встроенной панели регистрации консольных сообщений Console основного окна программного модуля iMPACT.

Для того чтобы очистить микросхему загрузочной Flash-памяти (перевести ее в незапрограммированное состояние), нужно воспользоваться командой Erase. В процессе ее выполнения осуществляется стирание всех данных, записанных ранее в загрузочное ППЗУ. Об успешном окончании этого процесса информирует всплывающая панель, содержащая сообщение Erase Succeeded (рис. 20).

Подготовка инструментального модуля для загрузки конфигурации аппаратной части разработанной микропроцессорной системы и программного обеспечения из Flash ППЗУ

Для осуществления загрузки конфигурации аппаратной части разработанной микропроцессорной системы и программного обеспечения из Flash ППЗУ необходимо на входы MIO2–MIO4 и MIO6 кристалла семейства Zynq‑7000 AP SoC подать сигнал низкого логического уровня. В то же время ко входу MIO5 кристалла расширяемой процессорной платформы должно быть приложено напряжение высокого логического уровня. При реализации разработанной встраиваемой системы на базе инструментального модуля ZedBoard [13] выбор требуемого режима загрузки достигается установкой коммутационных перемычек JP7–JP9 и JP11 в положение SIG-GND, а JP10 — в положение SIG‑3V3. После установки указанной комбинации коммутационных перемычек нужно подать напряжение питания на используемый инструментальный модуль. Дальнейший процесс загрузки конфигурации аппаратной части разработанной микропроцессорной системы и программного обеспечения из микросхемы Flash-памяти осуществляется таким же образом, как и при использовании карты памяти формата SD Card в качестве загрузочного устройства [27].

- Зотов В. Расширение семейства программируемых систем на кристалле Zynq‑7000 AP SoC // Компоненты и технологии. 2013. № 12. 2014. № 1.

- Zynq‑7000 All Programmable SoC Overview. Advance Product Specification. — Xilinx, 2013.

- Zynq‑7000 All Programmable SoC (XC7Z010, XC7Z015, and XC7Z020): DC and AC Switching Characteristics. — Xilinx, 2013.

- Zynq‑7000 All Programmable SoC (XC7Z030, XC7Z045, and XC7Z100): DC and AC Switching Characteristics. — Xilinx, 2013.

- Zynq‑7000 All Programmable SoC Technical Reference Manual. — Xilinx, 2013.

- Zynq‑7000 All Programmable SoC: Concepts, Tools, and Techniques (CTT) A Hands-On Guide to Effective Embedded System Design. — Xilinx, 2013.

- Zynq‑7000 All Programmable SoC Software Developers Guide. — Xilinx, 2013.

- Zynq‑7000 All Programmable SoC PCB Design and Pin Planning Guide. — Xilinx, 2013.

- 7 Series FPGAs and Zynq‑7000 All Programmable SoC XADC Dual 12‑Bit 1 MSPS Analog-to-Digital Converter User Guide. — Xilinx, 2012.

- Зотов В. Средства автоматизированного проектирования и этапы разработки встраиваемых микропроцессорных систем на базе расширяемых процессорных платформ семейства Zynq‑7000 AP SoC // Компоненты и технологии. 2014. № 2–3.

- Зотов В. Проектирование встраиваемых микропроцессорных систем на базе расширяемых процессорных платформ семейства Zynq‑7000 AP SoC в САПР Xilinx ISE Design Suite // Компоненты и технологии. 2014. № 4–12. 2015. № 1.

- Зотов В. Аппаратные средства разработки и отладки встраиваемых микропроцессорных систем, проектируемых на основе расширяемых вычислительных платформ фирмы Xilinx семейства Zynq‑7000 AP SoC // Компоненты и технологии. 2013. № 1.

- Зотов В. ZedBoard — эффективный инструмент разработки и отладки встраиваемых микропроцессорных систем, проектируемых на основе расширяемых вычислительных платформ фирмы Xilinx семейства Zynq‑7000 AP SoC // Компоненты и технологии. 2013. № 6.

- Зотов В. MicroZed — семейство унифицированных модулей для отладки и реализации встраиваемых микропроцессорных систем, проектируемых на основе платформ фирмы Xilinx серии Zynq‑7000 AP SoC // Компоненты и технологии. 2013. № 11.

- Embedded System Tools Reference Manual. — Xilinx, 2013.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 1 // Компоненты и технологии. 2015. № 2.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 2 // Компоненты и технологии. 2015. № 3.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 3 // Компоненты и технологии. 2015. № 4.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 4 // Компоненты и технологии. 2015. № 5.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 5 // Компоненты и технологии. 2015. № 6.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 6 // Компоненты и технологии. 2015. № 7.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 7 // Компоненты и технологии. 2015. № 8.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 8 // Компоненты и технологии. 2015. № 9.

- Зотов В. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М.: Горячая линия – Телеком, 2006.

- Зотов В. Инструментальный модуль компании Avnet для отладки проектов встраиваемых систем, разрабатываемых на базе нового семейства ПЛИС FPGA фирмы Xilinx Virtex‑5 FXT // Компоненты и технологии. 2008. № 9.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 9 // Компоненты и технологии. 2015. № 10.

- Зотов В. Разработка программного обеспечения встраиваемых микропроцессорных систем, проектируемых на базе расширяемых вычислительных платформ семейства Zynq‑7000 AP SoC фирмы Xilinx. Часть 10 // Компоненты и технологии. 2015. № 11.

4 августа, 2020

4 августа, 2020 17 мая, 2021

17 мая, 2021 27 июня, 2022

27 июня, 2022