Решение сложных интерфейсных задач с использованием мостов на микросхемах FPGA сверхнизкой плотности

Проектирование оптимизированных интерфейсных мостов

Безусловно, лишь немногие архитектуры способны обеспечить высочайшую гибкость, которая необходима для масштабирования в условиях стремительно меняющихся требований к вводу/выводу, особенно если нужно получить низкие энергопотребление и себестоимость. Исходя из этого, проектировщики реализуют разнообразные интерфейсные мосты, позволяющие передавать данные со сменой протоколов и попутно расширять функциональность систем. Трудность состоит в том, чтобы определить, как наиболее эффективно реализовывать такие новые решения, не выходя за рамки ограничений на потребляемую мощность, размеры и себестоимость системы.

В статье рассматриваются потенциальные способы решения таких задач путем реализации высокооптимизированных интерфейсных мостов на базе программируемых пользователем маломощных логических интегральных схем FPGA сверхнизкой плотности (Ultra Low Density, ULD), которые сочетают в себе гибкость программируемой платформы и высокую производительность при низком энергопотреблении.

Широкий спектр вариантов применения интерфейсных мостов

В зависимости от требований к производительности системы можно применять множество различных реализаций интерфейсных мостов. Конструкции невысокой производительности часто оснащаются несколькими интерфейсами, работающими на тактовой частоте ниже 50 МГц, такими как UART, I2C, I2S, SPI, USB, Microwire, SoundWire, карты памяти и ШИМ. Интерфейсные мосты в этих случаях разветвляют сигнал одного интерфейса (например, I2C) на несколько интерфейсов того же или иного стандарта.

Разумеется, с ростом тактовой частоты требования к интерфейсным мостам усложняются. Например, на рынках обработки изображений и связи, а также в науке, промышленности и на автомобильном производстве проектировщикам приходится искать новые способы экономически эффективного преобразования данных от одного протокола к другому. Типичные применения — встраивание новых высокоскоростных датчиков изображения в старые системы или переход с одного стандартного формата передачи данных на другой. Идеальным выбором будут решения с доказанной надежностью и экономической эффективностью при массовом производстве на высококонкурентных рынках.

Проектные компромиссы

Для преодоления сложностей, связанных с сопряжением интерфейсов в современных условиях, проектировщикам необходимо гибкое решение с малой длительностью цикла разработки, которое бы обеспечивало высокую скорость передачи данных и поддержку специализированных протоколов без увеличения сроков разработки, энергопотребления или себестоимости. К сожалению, большинство решений, представленных сегодня на рынке, не позволяет достичь этих целей. Например, интерфейсы ввода/вывода большинства микроконтроллеров ограничены по скорости. Вместе с тем многие из упомянутых выше высокоскоростных шин используют дифференциальную передачу сигналов и последовательный интерфейс, который при скорости передачи данных, доходящей до 500 Мбит/с, намного превосходит возможности популярных микроконтроллеров.

Более того, обычно в этих высокоскоростных шинах применяются собственные узкоспециализированные команды и коды синхронизации, не поддерживаемые большинством микроконтроллеров.

Хотя многие из распространенных микроконтроллеров поддерживают низкоскоростные интерфейсы, такие как I2C, SPI и ШИМ, реализация интерфейсного моста на микроконтроллере потребует существенных инвестиций в разработку кода. К тому же, представляя собой систему на основе прерываний, типовой микроконтроллер находится в явно невыгодном положении. Поступающее прерывание ставится в очередь, и в зависимости от того, какие еще задачи выполняются процессором, может возникнуть задержка, которая ставит под угрозу достоверность данных. Микроконтроллер, работающий в качестве моста, не может позволить прерыванию приостановить выполнение этой функции. Стало быть, единственный выход — это использовать микроконтроллер исключительно в роли моста, что в большинстве случаев существенно увеличит размеры, себестоимость и рассеиваемую мощность системы.

Специализированные ИС (ASIC) лучше подходят для применения в мостовых схемах с точки зрения производительности. Но длительный цикл разработки и большие единовременные затраты на проектирование делают их нерентабельными на рынке интерфейсных мостов. С помощью специализированных стандартных изделий (ASSP) можно получить более привлекательную структуру затрат, но таких изделий совсем немного, потому что производители не могут обосновать эти инвестиции в случае нестандартных решений. В конечном счете ввиду относительной негибкости любого решения с жестко заданной функциональностью большинство ASSP являются слишком узкоспециализированными для применения во многих интерфейсных мостах.

Микросхемы FPGA сверхнизкой плотности

Традиционно микросхемы FPGA воспринимались как слишком громоздкие, дорогие и неэкономичные для использования в мостах подобного рода. Однако новый класс устройств сверхнизкой плотности (ULD), разработанный компанией Lattice Semiconductor, стремительно меняет эти представления и открывает новые возможности для реализации оптимизированных мостовых решений. Воплощая в себе недавние достижения технического прогресса, направленные на уменьшение энергопотребления, размеров и себестоимости электронных устройств, микросхемы FPGA сверхнизкой плотности предоставляют проектировщикам уникальный набор преимуществ, которыми не обладают традиционные мостовые решения.

Первое и важнейшее преимущество — это гибкость в проектировании. Например, микросхемы FPGA сверхнизкой плотности компании Lattice Semiconductor позволяют выбирать количество линий ввода/вывода в широких пределах — от 21 до более чем 250. Поскольку каждая линия вывода в FPGA является программируемой, проектировщикам более не нужно корректировать требования к интерфейсам, чтобы уложиться в рамки ограничений прикладного процессора или ASSP. Используя микросхемы FPGA сверхнизкой плотности, они могут просто перепрограммировать интерфейсный мост под новые требования, реализовав интерфейсы любого вида на входе и выходе микросхемы. Высокая степень гибкости позволяет быстро и легко менять интерфейсы по мере эволюции конструкции изделия или интерфейсных стандартов, не меняя код в прикладном процессоре. А в случае перехода на нестандартные интерфейсы, для которых необходимы особые тактовые частоты и узкоспециализированные протоколы, возможность перепрограммировать интерфейс и переназначить логические ресурсы в соответствии с новыми требованиями обеспечивает проектировщикам систем особое преимущество.

При этом интерфейсный мост на микросхеме FPGA сверхнизкой плотности можно реализовать, не жертвуя энергопотреблением. За последние два десятилетия типичная потребляемая мощность микросхем FPGA снизилась очень сильно — с 0,5 Вт до менее чем 50 мкВт. Соответственно, мост на FPGA будет потреблять гораздо меньше электроэнергии, чем рядовой процессор. Но экономия электроэнергии достигается не только за счет этого. Реализовав мост в логике реального времени на базе микросхемы FPGA, а не процессора, работающего по прерываниям, проектировщику больше не нужно держать энергоемкий прикладной процессор все время включенным. FPGA может мгновенно откликаться на поступающие данные, освобождая прикладной процессор от выполнения затратных по времени операций управления мостом.

Наконец, микросхемы FPGA сверхнизкой плотности уже доказали свою надежность в самых высококонкурентных сегментах потребительского рынка. Эти компоненты, широко применяющиеся в популярных мобильных телефонах, продемонстрировали высочайший уровень качества и рентабельности, который требуется при производстве массовой продукции потребительского назначения.

Примеры применения

Приведенные далее примеры конструкций показывают, как коллективы разработчиков могут использовать характерные преимущества микросхем FPGA сверхнизкой плотности для реализации интерфейсных мостов.

Мост IR–I2C

Первым примером будет мост IR–I2C (рис. 1). В нем используется микросхема FPGA iCE40LP1K компании Lattice Semiconductor в компактном корпусе WLCSP с 36 выводами, которая обеспечивает сопряжение модуля инфракрасного приемника Vishay TSOP34338 или TSOP98200 с платой на базе процессора Qualcomm APQ8060. APQ8060 не имеет выводов для инфракрасного интерфейса, поэтому iCE40LP1K будет оптимальным выбором для сопряжения этого интерфейса с шиной I2C.

Типичный потребляемый ток iCE40LP1K в статическом режиме — всего 40 мкА. При необходимости в этой конструкции моста хватит ресурсов, чтобы реализовать дополнительные выводы для управления двумя инфракрасными передатчиками. Разные варианты этой схемы позволяют обеспечить поддержку различных пультов дистанционного управления или инфракрасных приемников.

Мост на два датчика изображения

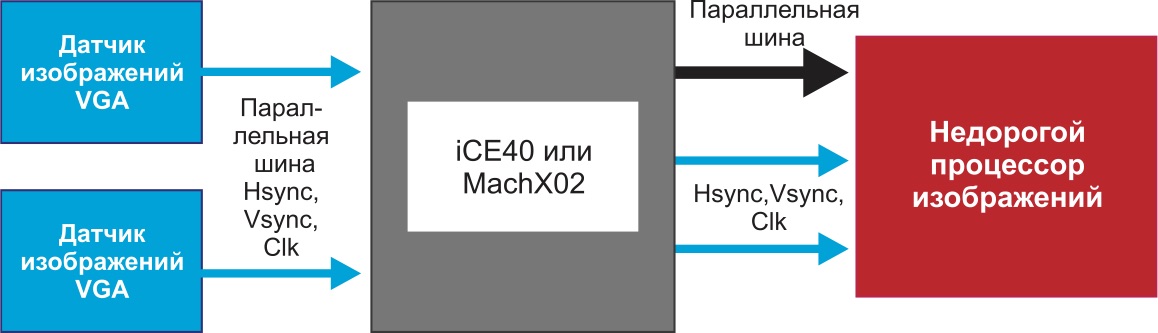

В настоящее время наблюдается рост числа изделий с применением нескольких датчиков изображения. Это, в частности, трехмерная стереоскопическая видеоаппаратура, устройства анализа трехмерных изображений для систем охраны и видеонаблюдения, автомобильные видеорегистраторы. Многие распространенные сейчас процессоры изображений имеют только один порт датчика изображений, но по своей производительности способны обрабатывать данные от двух датчиков при условии правильного сопряжения. Чтобы увеличить число портов процессора изображений, проектировщики используют мост на два датчика.

На рис. 2 приведена типовая схема моста на два датчика изображений для автомобильного видеорегистратора. В этих системах обычно используется две камеры: одна направлена на лобовое стекло, а вторая — на водителя. Мост реализован на базе микросхемы FPGA сверхнизкой плотности Mach X02-1200 компании Lattice Semiconductor. Эта микросхема обеспечивает синхронизацию и управление изображениями с двух датчиков, а также вывод данных в формате, который поддерживается процессором изображений. Микросхема FPGA X02-1200 предоставляет до 1200 таблиц подстановки и до 108 линий ввода/вывода. Она также содержит блоки I2C, SPI и таймер-счетчик с дополнительной защитой. Показанный на рис. 2 мост поддерживает работу с двумя датчиками изображения разрешением до 720p каждый. Формат вывода данных на процессор изображений — либо «верх/низ», либо «право/лево».

Мост GMII–RGMII

Еще одной популярной функцией интерфейсных мостов является поддержка меняющихся стандартов. GMII — это широко применяемый стандарт интерфейса Ethernet. Но в более новых конструкциях внедряется интерфейс RGMII, который был разработан с целью снижения стоимости за счет уменьшения числа выводов с 22 до 12.

На рис. 3 показана схема двунаправленного моста GMII–RGMII на базе микросхемы FPGA компании Lattice Semiconductor. Мост работает на тактовой частоте более 125 МГц и использует линии ввода/вывода HSTL без дополнительных буферов. Выводы разделены на сторону GMII и сторону RGMII. Данные передаются с удвоенной скоростью, что позволяет осуществлять передачу по положительному и отрицательному фронтам тактового сигнала.

В микросхеме FPGA имеются сдвиговые регистры ввода/вывода (IOSR) для каждой группы программируемых линий ввода/вывода (PIO), настроенных для синхронной работы и передачи данных по обоим фронтам тактового сигнала.

Мост для сопряжения датчика изображений MIPI CSI-2 с параллельным КМОП-интерфейсом

С ростом потребительского спроса на встроенные камеры в смартфонах все большую популярность завоевывает последовательный интерфейс камеры MIPI CSI-2. Эта спецификация предусматривает высокоскоростной интерфейс с низким энергопотреблением между периферийной камерой и главным процессором. Благодаря своим высоким характеристикам и низкой стоимости датчики изображений, соответствующие стандарту CSI-2, находят сегодня широкое применение во встраиваемых системах. Но большинство процессоров изображений, которые на данный момент используются в этих системах, оснащены традиционным параллельным КМОП-интерфейсом, который требует большого числа соединений и потребляет относительно много энергии. Такие процессоры нельзя напрямую соединить с датчиком изображений, имеющим интерфейс CSI-2.

Рис. 4. Мост для сопряжения датчика изображений MIPI CSI-2 с параллельной шиной на базе микросхемы FPGA MachX02

На рис. 4 показана схема моста для сопряжения датчика изображений MIPI CSI-2 с параллельной шиной. Она поддерживает высокоскоростную дифференциальную передачу сигналов CSI-2 по линиям данных (от одной до четырех) на скорости до 750 Мбит/с. Этот мост, реализованный на базе микросхемы FPGA Mach X02 компании Lattice Semiconductor, поддерживает синфазное напряжение 200 мВ в высокоскоростном режиме с использованием дифференциальных входных контактных площадок. Он также обеспечивает вывод на параллельный интерфейс датчика изображения в форматах RAW, RGB и YUV с разрядностью от 6 до 24 бит. Обычно такой мост синтезируется в одиночном формате CSI-2 для минимизации размеров микросхемы FPGA. Он позволяет обеспечить поддержку нескольких форматов CSI-2 с переключением между ними «на лету» при добавлении нескольких экземпляров MIPI CSI-2 Serial2Parallel NGO в каждом из нужных форматов.

Ретранслятор сигналов датчика изображений

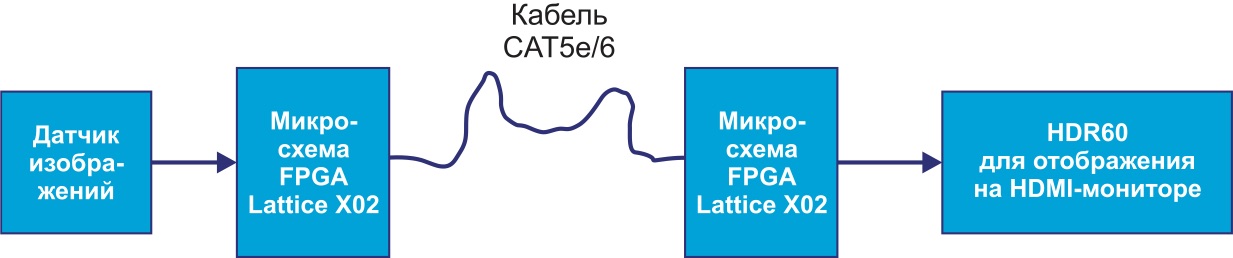

В ряде применений, например в установках неразрушающего контроля труб, медицинских датчиках и некоторых автомобильных камерах сторонних производителей, датчик изображений располагается на значительном удалении от процессора изображений. Для этих случаев компания Lattice Semiconductor разработала ретранслятор сигналов датчика изображений на базе двух микросхем FPGA Mach X02 (рис. 5). Одна из них расположена рядом с датчиком изображений и служит для сериализации сигнала, а другая — рядом с процессором изображений и служит для десериализации сигнала. Друг с другом они соединяются одиночным кабелем Ethernet CAT5e/6.

Рис. 5. Ретранслятор сигналов датчика изображений на базе двух микросхем FPGA Lattice X02 и кабеля Cat5e/6

Датчик изображений может работать в формате 720p60 или 1080p30 и находиться на расстоянии до 8 м при использовании хорошо согласованных пар. Интерфейс к процессору изображений после десериализации может быть параллельным или последовательным. Параллельные интерфейсы можно сконфигурировать для работы при различных уровнях напряжения низковольтной КМОП-логики (LVCMOS), включая 1,8, 2,5 и 3,3 В. Ретранслятор может быть с двумя и более датчиками изображений. В числе прочего он допускает сопряжение с датчиками изображений, имеющими параллельный интерфейс, а также интерфейсы CSI-2, HiSPi и sub-LVDS.

Заключение

С расширением функциональности проектируемых систем требования к возможностям ввода/вывода будут расти. Мостовые решения представляют собой практичный способ расширения возможностей ввода/вывода в системах старой архитектуры. Микросхемы FPGA сверхнизкой плотности — это чрезвычайно гибкая платформа для реализации интерфейсов ввода/вывода различного типа и разной пропускной способности, предоставляющая проектировщикам уникальную возможность создавать оптимизированные мостовые решения с низким энергопотреблением для систем нового поколения.

4 августа, 2020

4 августа, 2020 27 июня, 2022

27 июня, 2022 2 декабря, 2020

2 декабря, 2020