Проектирование КИХ-фильтров с учетом архитектурных особенностей ПЛИС

На рис. 1 показаны структуры фильтров, характерные для реализации в базисе сигнальных цифровых процессоров, а на рис. 2 — структуры фильтров, характерные для реализации в базисе ПЛИС [1]. В качестве матричных умножителей могут быть применены параллельные векторные умножители. На рис. 3а представлен 2‑разрядный векторный умножитель с использованием двух идентичных таблиц перекодировки LUT1 и LUT2 для формирования частичных произведений P1(n) и P2(n), которые необходимо сложить с учетом их веса. Каждая LUT образована из четырех LUT логических элементов (ЛЭ) ПЛИС. Результат вычисления P2(n) необходимо сдвинуть на один разряд влево. Такой умножитель может быть использован для структуры фильтра 4 отвода 2 бита, при 2‑разрядном представлении коэффициентов. В случае если число отводов останется постоянным (например, 4, в случае симметрии коэффициентов фильтра), а разрядность входного сигнала, подлежащего фильтрации, и коэффициентов фильтра составит 8 бит, то уже потребуется 8 LUT, каждая из которых будет содержать 8 LUT ЛЭ. При этом увеличивается и число многоразрядных сумматоров и операций сдвига (рис. 4).

Рис. 1. Фильтры на четыре отвода для реализации в базисе цифровых сигнальных процессоров:

а) параллельный;

б) последовательный

![Параллельный векторный умножитель четырех 2 разрядных сигналов на четыре 2 разрядные константы с использованием LUT ЛЭ в ПЛИС серии FLEX [2]](https://fpga-e.ru/wp-content/uploads/01_157-03-600x415.jpg)

Рис. 3. Параллельный векторный умножитель четырех 2 разрядных сигналов на четыре 2 разрядные константы с использованием LUT ЛЭ в ПЛИС серии FLEX [2]

Параллельные КИХ-фильтры, реализованные в базисе ПЛИС, обладая наивысшим быстродействием, позволяют получать результат фильтрации, например, для КИХ-фильтра со структурой 120 отводов 12 бит, уже после первого синхроимпульса, последовательные — через 12, а фильтр в базисе ЦОС-процессоров — через 120 синхроимпульсов [1].

![Параллельный векторный умножитель четырех 8 разрядных сигналов на четыре 8 разрядные константы с использованием LUT ЛЭ в ПЛИС серии FLEX [2]](https://fpga-e.ru/wp-content/uploads/01_157-04-600x861.jpg)

Рис. 4. Параллельный векторный умножитель четырех 8 разрядных сигналов на четыре 8 разрядные константы с использованием LUT ЛЭ в ПЛИС серии FLEX [2]

Рис. 5 показывает использование параллельного векторного умножителя четырех 8‑разрядных сигналов на четыре 8‑разрядные константы в составе КИХ-фильтра на 8 отводов с симметричными коэффициентами [4]. Симметричность коэффициентов позволяет применить пресумматоры на выходах линии задержки, что и обеспечит формирование четырех 8‑разрядных сигналов. Рис. 6а демонстрирует число задействованных конфигурируемых логических блоков (КЛБ) для реализации параллельного векторного умножителя в базисе ПЛИС серии XC4000. Для симметричного КИХ-фильтра со структурой 8 отводов 8 бит с точностью представления коэффициентов 8 бит потребуется 122 КЛБ ПЛИС серии XC4000 фирмы Xilinx, при этом обеспечивается быстродействие 50–70 MSPS [4].

![Использование параллельного векторного умножителя четырех 8 разрядных сигналов на четыре 8 разрядные константы в составе КИХ-фильтра на 8 отводов с симметричными коэффициентами в базисе ПЛИС XC4000, построенного с применением параллельной распределенной арифметики [4]](https://fpga-e.ru/wp-content/uploads/01_157-05-600x363.jpg)

Рис. 5. Использование параллельного векторного умножителя четырех 8 разрядных сигналов на четыре 8 разрядные константы в составе КИХ-фильтра на 8 отводов с симметричными коэффициентами в базисе ПЛИС XC4000, построенного с применением параллельной распределенной арифметики [4]

![Число задействованных ресурсов для реализации параллельного векторного умножителя в базисе ПЛИС XC4000 [4] (а) и производительность фильтра (б) в зависимости от числа отводов, при частоте тактирования 120 МГц [5]](https://fpga-e.ru/wp-content/uploads/01_157-06.jpg)

Рис. 6. Число задействованных ресурсов для реализации параллельного векторного умножителя в базисе ПЛИС XC4000 [4] (а) и производительность фильтра (б) в зависимости от числа отводов, при частоте тактирования 120 МГц [5]

В случае последовательной структуры (рис. 2б) применяется одна-единственная LUT для вычисления частичных произведений (рис. 7). Такой фильтр обрабатывает только один разряд входного сигнала в течение такта. Последовательно вычисляемые частичные произведения накапливаются в масштабирующем аккумуляторе. После N для несимметричного и N+1 тактов синхроимпульсов для симметричного фильтра на выходе появляется результат, где N — разрядность входного сигнала, подлежащего фильтрации. Для обеспечения правильной работы фильтра требуется управляющий автомат.

Рис. 7. Симметричный КИХ-фильтр со структурой 10 отводов 10 бит с точностью представления коэффициентов 10 бит с использованием последовательной распределенной арифметики

Производительность фильтра определяется как fclk/N для несимметричного и как fclk/N+1 для симметричного фильтра [5]. Рис. 6б показывает, что с ростом числа отводов производительность фильтра остается постоянной, в то время как у фильтра на базе ЦОС-процессора с использованием MAC-блоков она начинает резко падать при числе отводов более 16.

Рассмотрим особенности проектирования КИХ-фильтра на основе параллельной распределенной арифметики на примере структуры четыре отвода четыре бита. Ранее такая структура фильтра использовалась в работах [6, 7, 8, 9]. Коэффициенты фильтра возьмем целочисленными, со знаком, равными C0 = –2, C1 = –1, C2 = 7 и C3 = 6, то есть как в работах [6, 7, 8, 9]. Для сохранения общности будем также считать, что на вход КИХ-фильтра поступают входные отсчеты –5, 3, 1 и 0. Правильные значения на выходе фильтра: 10, –1, –40, –10, 26, 6 и т. д. Исследования проведем на ПЛИС Cyclone III EP3C5E144C7. Главный критерий отбора — максимальная частота/частота, в наихудшем случае определенная по модели Slow 1200mV 85 С («медленная» модель, при напряжении VCC 1100 мВ и температуре +85 °C) путем проведения статического временного анализа.

В тестировании принимают участие следующие структуры фильтров: классическая параллельная с использованием аппаратных ЦОС-боков (собраны на мегафункции ALTMULT_ADD, [6]); систолическая структура [9]; поведенческое описание на языке VHDL с использованием оператора цикла без привязки к какой-либо структуре [7] посредством программных умножителей (мегафункция ALTMEMMULT) [6] и «готовый» фильтр на параллельной распределенной арифметике, реализованный с помощью мегаядра MegaCore FIR Compiler [8].

Уравнение КИХ-фильтра со структурой четыре отвода четыре бита (прямая реализация) представляется как арифметическая сумма произведений [3]:

Pout = C1d1+C2d2+C3d3+C4d4.

В случае параллельной распределенной арифметики уравнение КИХ-фильтра на четыре отвода записывается в виде [3]:

Pout = 20×P0+21×P1+22×P2+23×P3. (1)

Частичные произведения P0, P1, P2 и P3:

В случае параллельной распределенной арифметики для КИХ-фильтра на четыре отвода необходимо иметь четыре идентичных массива памяти, параллельно адресуемых всеми битами всех входных переменных, и свертывающее иерархическое дерево многоразрядных сумматоров, осуществляющих соответствующее суммирование частичных произведений P0, P1, P2 и P3. В данном случае результат формируется за один такт и тем самым достигается наибольшее быстродействие структуры.

На рис. 8 показана линия задержки КИХ-фильтра, а на рис. 9 изображен принцип подключения выходов линии задержки КИХ-фильтра на 4 отвода к 4‑входовым LUT [3]. Разрядность входной шины данных N = 4. Входные данные на линии задержки представлены с 4‑битной точностью параллельным кодом. 4‑входовая LUT обеспечивает 16 частичных произведений (на примере P0, представляющих собой комбинации сумм коэффициентов фильтра, показанных с 8‑битной точностью).

![Принцип подключения выходов линии задержки КИХ-фильтра на четыре отвода к 4 входовым LUT [3]](https://fpga-e.ru/wp-content/uploads/01_157-09-600x236.jpg)

Рис. 9. Принцип подключения выходов линии задержки КИХ-фильтра на четыре отвода к 4 входовым LUT [3]

Пример заполнения 4‑входовой LUT есть в таблице 1, а описание на языке VHDL представлено ниже. На рис. 10 можно увидеть КИХ-фильтр со структурой четыре отвода четыре бита на распределенной параллельной арифметике. Фильтр состоит из четырех однотипных LUT, формирующих частичные произведения P0, P1, P2 и P3 согласно формулам (2–5). Для суммирований значений с выходов LUT в соответствии с их весом (формула (1)) используются два 12‑ и один 14‑разрядный сумматор с соответствующей коррекцией разрядности на входах, для того чтобы гарантированно предотвратить переполнение.

Рис. 10. КИХ-фильтр со структурой четыре отвода четыре бита на распределенной параллельной арифметике

|

d4(0) d3(0) d2(0) d1(0) |

Выход LUT-таблицы, P0 |

|

0000 |

0 |

|

0001 |

С1 |

|

0010 |

С2 |

|

0011 |

С2+С1 |

|

0100 |

С3 |

|

…. |

…. |

|

1111 |

С4+С3+С2+С1 |

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

Entity PartialProd is

Port (D : in std_logic_vector(3 downto 0);

P : out std_logic_vector(9 downto 0));

-- 4 * 8 bit coeff => 10 bit product

End PartialProd;

Architecture Behave of PartialProd is

constant c1 : std_logic_vector := "11111110"; -- coefficient for tap 1

-- -2D

constant c2 : std_logic_vector := "11111111"; -- coefficient for tap 2

-- -1D

constant c3 : std_logic_vector := "00000111"; -- coefficient for tap 3

-- 7D

constant c4 : std_logic_vector := "00000110"; -- coefficient for tap 4

-- 6D

-- Compute all the partial products and store them as constants.

constant v0 : std_logic_vector := sxt("0", 10);

constant v1 : std_logic_vector := sxt(c1, 10);

constant v2 : std_logic_vector := sxt(c2, 10);

constant v3 : std_logic_vector := v1 + v2;

constant v4 : std_logic_vector := sxt(c3, 10);

constant v5 : std_logic_vector := v4 + v1;

constant v6 : std_logic_vector := v4 + v2;

constant v7 : std_logic_vector := v4 + v3;

constant v8 : std_logic_vector := sxt(c4, 10);

constant v9 : std_logic_vector := v8 + v1;

constant v10 : std_logic_vector := v8 + v2;

constant v11 : std_logic_vector := v8 + v3;

constant v12 : std_logic_vector := v8 + v4;

constant v13 : std_logic_vector := v8 + v5;

constant v14 : std_logic_vector := v8 + v6;

constant v15 : std_logic_vector := v8 + v7;

Begin

prodeval: process (D)

begin

case(d) is

when "0000" => P <= v0;

when "0001" => P <= v1;

when "0010" => P <= v2;

when "0011" => P <= v3;

when "0100" => P <= v4;

when "0101" => P <= v5;

when "0110" => P <= v6;

when "0111" => P <= v7;

when "1000" => P <= v8;

when "1001" => P <= v9;

when "1010" => P <= v10;

when "1011" => P <= v11;

when "1100" => P <= v12;

when "1101" => P <= v13;

when "1110" => P <= v14;

when "1111" => P <= v15;

end case;

end process;

end behave;

Листинг. Пример описания заполнения LUT на языке VHDL для КИХ-фильтра на четыре отвода

На рис. 11 показана функциональная модель КИХ‑фильтра со структурой четыре отвода четыре бита на распределенной параллельной арифметике в САПР ПЛИС Quartus II с использованием линии задержки на регистрах (рис. 11а) и линии задержки на базе встроенных блоков ОЗУ (рис. 11б). Мегафункция ALTSHIFT_TAPS, используемая в качестве линии задержки, представляет собой двухпортовое ОЗУ. Свертывающее иерархическое дерево многоразрядных сумматоров выполнено на мегафункциях LPM_ADD_SUB. Для знакового разряда (P3) необходимо сформировать дополнение до двух путем обращения P3 с последующим прибавлением 1 к младшему разряду.

Рис. 11. КИХ-фильтр со структурой четыре отвода четыре бита на распределенной параллельной арифметике в САПР ПЛИС Quartus II:

а) линия задержки на регистрах;

б) линия задержки на базе встроенных блоков ОЗУ; в) частичные произведения на базе LUT и свертывающее иерархическое дерево многоразрядных сумматоров

Обращение логически эквивалентно инверсии каждого бита в числе. Вентили «исключающее ИЛИ» можно применить для избирательной инверсии в зависимости от значения управляющего сигнала. Прибавление «1» можно организовать подключением входа переноса Cin одного из 12‑разрядного сумматора к шине питания.

Рис. 12. Прохождение единичного импульса по структуре КИХ-фильтра в случае использования линии задержки на регистрах

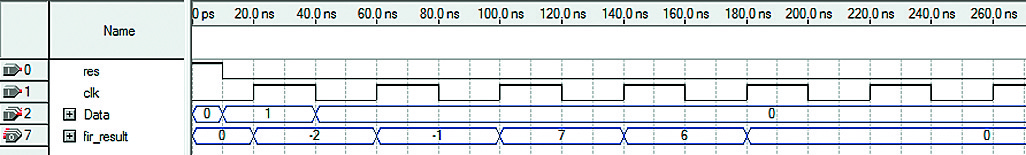

Прохождение единичного импульса по структуре КИХ-фильтра в случае использования линии задержки на регистрах показано на рис. 12. На выходе фильтра видим коэффициенты фильтра C0 = –2, C1 = –1, C2 = 7 и C3 = 6. На рис. 13 показаны временные диаграммы работы фильтра для случая, когда на вход КИХ-фильтра поступают входные отсчеты –5, 3, 1 и 0. Правильные значения на выходе фильтра: 10, –1, –40, –10, 26, 6 и т. д. На рис. 14 и 15 представлены временные диаграммы в случае использования линии задержки на базе встроенных блоков ОЗУ.

Рис. 13. Временные диаграммы работы фильтра в случае использования линии задержки на регистрах (на вход КИХ-фильтра поступают входные отсчеты –5, 3, 1 и 0; правильные значения на выходе фильтра: 10, –1, –40, –10, 26, 6 и т. д.)

Рис. 14. Прохождение единичного импульса по структуре КИХ-фильтра в случае использования линии задержки на базе встроенных блоков ОЗУ

Рис. 15. Временные диаграммы работы фильтра в случае использования линии задержки на базе встроенных блоков ОЗУ

Выводы

Рассмотрев основные структурные схемы параллельных КИХ-фильтров, можно сделать вывод, что использование КИХ-фильтров на параллельной распределенной арифметике позволяет для ПЛИС серии Cyclone III получить рекордное быстродействие за счет «безумножительных» схем умножения (табл. 2), не снижаемое при увеличении числа отводов фильтра и точности представления входных данных. Это особенно актуально для проектов, содержащих низкопроизводительные (бюджетные) серии ПЛИС, а также в том случае, если в проекте решено отказаться от мегафункций умножителей, опционально использующих либо аппаратные умножители, встроенные в ЦОС-блоки (ALTMULT_ADD, ALTMULT_ACCUM), либо программные (ALTMEMMULT). Применение кода языка VHDL и ядра FIR Compiler (структура фильтра задается опционально) в отличие от фильтров, структура которых разрабатывается пользователем «вручную», приводит к пониженному быстродействию, однако при этом необходимо учитывать, что рассматриваемые примеры сильно упрощены. Для точной оценки производительности фильтров необходимо прибегнуть к помощи сравнительных таблиц из официальных документов, например таблицы 3 из [1].

|

Ресурсы ПЛИС |

Параллельная распределенная арифметика (рис. 11). Линия задержки на |

Параллельная распределенная |

Мегафункция ALTMULT_ADD. 4 умножителя и дерево сумматоров в блоке, внешняя линия задержки из трех регистров [6] |

Систолический КИХ-фильтр с однотипными процессорными элементами [9] |

КИХ-фильтр разработан на языке VHDL с использованием оператора цикла loop [7] |

Мегафункция ALTMEMMULT, |

|

|

регистрах |

ОЗУ |

||||||

|

Количество логических элементов |

56 |

44 |

382 |

41 |

165 |

54 |

166 |

|

Количество LUT для реализации комбинационных функций |

40 |

44 |

342 |

29 |

132 |

42 |

146 |

|

Количество регистров для реализации последовательностной логики |

16 |

4 |

253 |

22 |

65 |

22 |

116 |

|

Аппаратные ЦОС-блоки, встроенные в базис ПЛИС |

0 (без использования мегафункций) |

0 |

0 |

4 (умножитель 9×9) |

0 (мегафункция LPM_MULT, умножители реализованы на LUT, |

0 |

0 (режим auto, 1 умножитель 4×4 занимает 20 lut+256 bits(Auto)+29 reg) |

|

Максимальная частота/частота в наихудшем случае, МГц (временная модель Slow 1200mV 85С Model) |

807/250 |

305/205 |

89/24 |

233/233 |

206/206 |

182/182 |

300/250 |

К недостаткам следует отнести возрастание числа задействованных ресурсов ПЛИС для КИХ-фильтров с большим числом отводов и точностью представления коэффициентов (табл. 3), поэтому по возможности нужно применять симметричные фильтры. Линия задержки на блочной памяти ПЛИС также позволяет сократить число используемых логических элементов. Последовательная распределенная арифметика снижает объем задействованных ресурсов ПЛИС, но ухудшает быстродействие и производительность фильтров.

|

LUT для реализации комбинационных функций |

Регистры ЛЭ для последовательной логики |

Память |

Умножители |

Fmax, МГц |

Быстродействие, MSPS |

|

|

Регистры ЛЭ, бит |

Блоки памяти M9K |

|||||

|

Параллельная распределенная арифметика с использованием ресурсов логических элементов, уровень конвейеризации 1, EP3C10F256C6 |

||||||

|

3416 |

3715 |

208 |

3 |

– |

288 |

288 |

|

Параллельная распределенная арифметика с использованием ресурсов встроенных блоков памяти M9K, уровень конвейеризации 1, EP3C40F780C6 |

||||||

|

1948 |

2155 |

120030 |

48 |

– |

283 |

283 |

|

Последовательная распределенная арифметика с использованием ресурсов встроенных блоков памяти M9K, уровень конвейеризации 1, EP3C10F256C6 |

||||||

|

327 |

462 |

14167 |

8 |

– |

323 |

36 |

- FIR Compiler. User Guide. Software Version: 11.0. May 2011. Altera Corporation.

- Application Note 73 Implementing FIR Filters in FLEX Devices, February 1998, ver 1.01.

- Application Note AC120. Designing FIR Filters with Actel FPGAs.

- Bruce Newgard. Seminar. Signal processing with XILINX FPGAs. June 9, 1996. xdsp.ppt. XILINX Hardware Digital Signal Processing.

- xilinx.com. DS240 April 28, 2005. Product Specification. Distributed Arithmetic FIR Filter v9.0.

- Строгонов А., Быстрицкий А. Проектирование параллельных КИХ-фильтров в базисе ПЛИС // Компоненты и технологии. 2013. № 6.

- Строгонов А., Быстрицкий А. КИХ-фильтр на распределенной арифметике: проектируем сами // Компоненты и технологии. 2013. № 3.

- Строгонов А. КИХ-фильтры на параллельной распределенной арифметике // Компоненты и технологии. 2013. № 5.

- Строгонов А., Быстрицкий А. Систолические КИХ-фильтры в базисе ПЛИС // Компоненты и технологии. 2013. № 8.

![Линия задержки КИХ-фильтра на регистрах [3]](https://fpga-e.ru/wp-content/uploads/01_157-08-600x146.jpg)

4 августа, 2020

4 августа, 2020 27 июня, 2022

27 июня, 2022 15 июня, 2020

15 июня, 2020