Моделирование цифровых устройств и встраиваемых микропроцессорных систем, проектируемых на основе ПЛИС фирмы Xilinx в интегрированной среде разработки PlanAhead.

Часть 2

Установка параметров генерации списков соединений моделируемого устройства или аппаратной части встраиваемой микропроцессорной системы

Для того чтобы установить требуемые значения параметров, используемых при генерации списков соединений моделируемого устройства или аппаратной части встраиваемой микропроцессорной системы, нужно открыть вкладку Netlist страницы Simulation диалоговой панели Project Settings, как показано на рис. 1.

Опция командной строки —insert_pp_buffers позволяет включать в формируемый список соединений модели разрабатываемого устройства или аппаратной части встраиваемой микропроцессорной системы буферные элементы, предотвращающие поглощение импульсов на входах компонентов, длительность которых меньше входной задержки. По умолчанию индикатор состояния этой опции находится в положении «Включено», разрешающем добавление в состав списка соединений дополнительных буферных элементов.

Опция командной строки -fn управляет преобразованием иерархической структуры объектов HDL-описаний проекта в генерируемом списке соединений формируемой модели. Если индикатор состояния этой опции установлен в положение «Выключено», то указанные объекты сохраняются в создаваемом списке соединений в виде отдельных иерархических модулей, соответствующих исходному описанию проекта. При включенном положении индикатора состояния рассматриваемой опции в процессе генерации списка соединений производится преобразование иерархической структуры объектов, представленной в исходном описании проектируемого устройства или встраиваемой микропроцессорной системы, к одноуровневому виду. По умолчанию индикатор состояния опции командной строки -fn находится в положении «Выключено», при котором сохраняется иерархическая структура объектов в создаваемом списке соединений формируемой модели.

С помощью опции командной строки -a определяется состав формируемого описания модели проектируемого устройства или встраиваемой микропроцессорной системы. Если индикатор состояния данной опции находится в положении «Включено», то в составе генерируемого описания будет присутствовать только блок определения архитектуры соответствующего объекта. В таком случае блок декларации этого объекта и описание его интерфейса не включается в формируемую модель. При выключенном состоянии индикатора -a, установленном по умолчанию, генерируется полное описание соответствующего объекта.

Опция командной строки -sdf_anno управляет включением конструкции $sdf_annotate в каждый формируемый файл списка соединений на языке Verilog. По умолчанию индикатор состояния, определяющий значение этой опции, установлен в положение «Выключено», при котором указанная конструкция не записывается в формируемые файлы.

Опция командной строки -tm предоставляет возможность изменять название объекта, соответствующего верхнему уровню иерархии в генерируемом списке соединений моделируемого устройства или аппаратной части встраиваемой микропроцессорной системы. По умолчанию, когда значение этой опции не определено, имя объекта верхнего уровня иерархии наследуется из модуля исходного описания проекта. Чтобы указать другой идентификатор, нужно активизировать поле редактирования значения рассматриваемого параметра и воспользоваться клавиатурой.

Значение опции командной строки -extid определяет возможность записать идентификаторы в расширенном формате в формируемом VHDL-описании модели, если в исходном файле эти идентификаторы представлены в указанной форме.

С помощью опции командной строки -sdf_path указывается раздел, в котором содержатся требуемые файлы SDF. Этот параметр применяется только в тех случаях, когда необходимые файлы SDF расположены вне рабочего каталога проекта моделируемого устройства или встраиваемой микропроцессорной системы. По умолчанию в качестве значения этой опции используется рабочий каталог проекта. Для выбора иного раздела следует расположить курсор в правой части строки рассматриваемой опции и щелкнуть левой кнопкой мыши. После этого появляется диалоговая панель с заголовком Select Directory (рис. 1), которая позволяет быстро найти и указать требуемый раздел.

Опция командной строки -ism разрешает или запрещает включение модулей библиотеки SIMPRIM в состав каждого формируемого файла списка соединений на языке Verilog. По умолчанию индикатор состояния этой опции находится в положении «Выключено», запрещающем добавление модулей библиотеки SIMPRIM в состав списка соединений генерируемой модели.

С помощью параметра More NetGen Options можно указать дополнительные опции командной строки для программы NETGEN. Для этого следует активизировать поле редактирования значения данного параметра, поместив курсор в правой части соответствующей строки и щелкнув левой кнопкой мыши. Требуемые опции командной строки указываются с помощью клавиатуры непосредственно в поле редактирования. Кроме того, дополнительные опции командной строки для программы NETGEN могут быть записаны в пакетный файл, идентификатор которого определяется в поле редактирования значения параметра More NetGen Options.

Определение дополнительных параметров моделирования разрабатываемого устройства или встраиваемой микропроцессорной системы

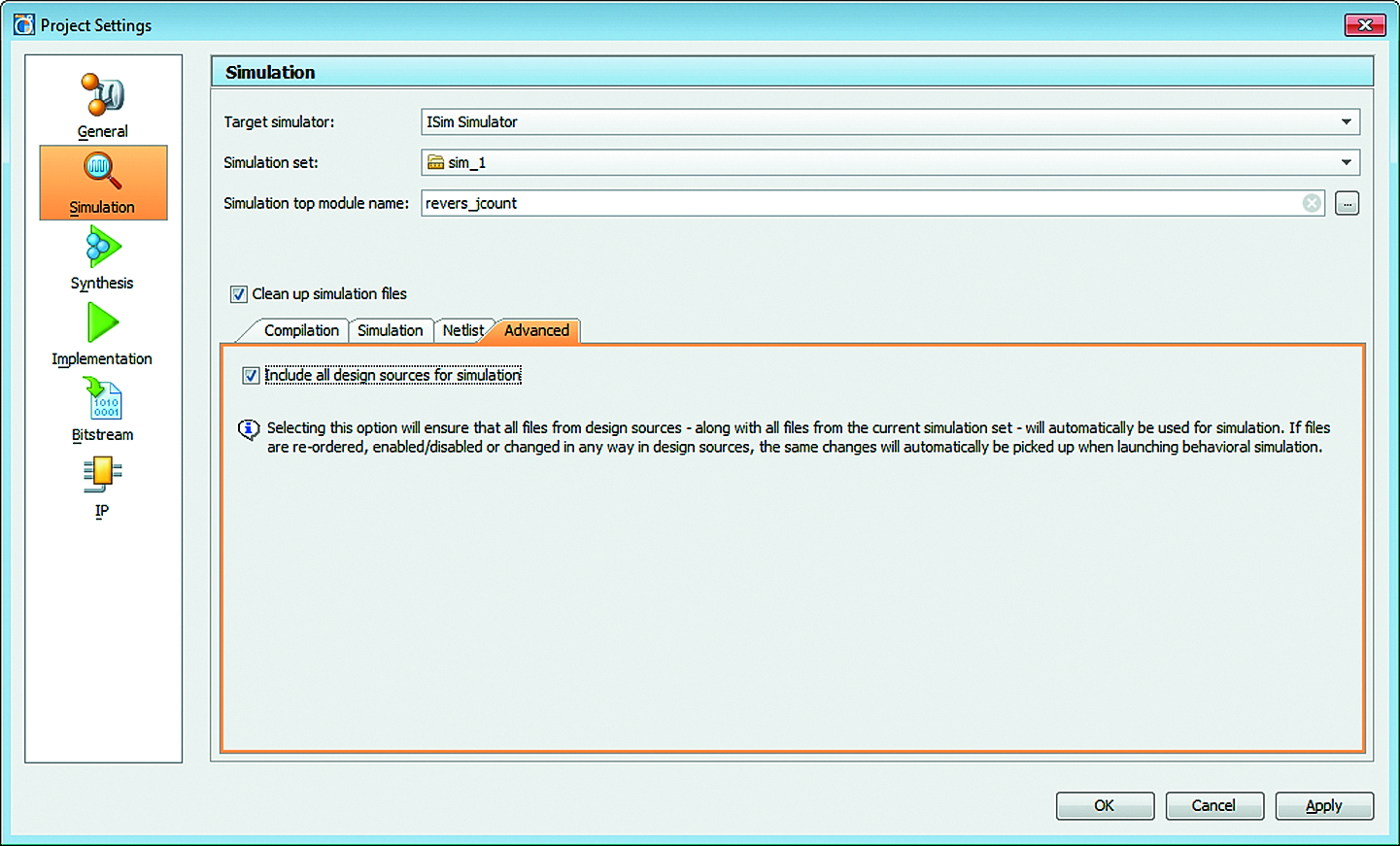

Для установки значений дополнительных параметров моделирования проектируемого устройства или встраиваемой микропроцессорной системы необходимо открыть вкладку Advanced страницы Simulation диалоговой панели Project Settings, чей вид представлен на рис. 2.

На этой вкладке представлен единственный параметр — Include all design sources for simulation, который предоставляет возможность использовать в ходе моделирования все исходные модули описания разрабатываемого устройства или аппаратной части встраиваемой микропроцессорной системы. Для выборочного включения модулей исходного описания в состав списка, предназначенного для осуществления моделирования проектируемого устройства или встраиваемой микропроцессорной системы, следует перевести индикатор состояния указанного параметра в положение «Выключено».

После установки нужных значений параметров, представленных на вкладках Compilation, Simulation [17], Netlist и Advanced страницы Simulation диалоговой панели Project Settings, надо подтвердить их нажатием клавиши Apply или ОК, расположенной в нижней части диалоговой панели Project Settings (рис. 1, 2).

Выполнение этапа поведенческого моделирования проектируемого устройства или встраиваемой микропроцессорной системы

Для выполнения этапа поведенческого моделирования проектируемого устройства или встраиваемой микропроцессорной системы нужно воспользоваться командой Run Behavioral Simulation, представленной в разделе Project Manager панели управления основными процессами, выполняемыми в ходе проектирования, Flow Navigator (рис. 3). Аналогичная команда содержится и во всплывающем меню Simulation, доступ к которому открывает одноименная строка всплывающего меню Tools.

При выборе указанной команды на экране появляется диалоговая панель с заголовком Launch Behavioral Simulation (рис. 3). Открывшаяся диалоговая панель позволяет выбрать объект верхнего уровня иерархии и комплект тестовых модулей для выполнения этапа поведенческого моделирования, а также указать параметры этого процесса, которые отличаются от предлагаемых по умолчанию. Набор тестовых модулей проекта, предназначенных для поведенческого моделирования, определяется в поле выбора значения параметра Simulation set. Процедура создания и выбора тестовых модулей проекта была подробно рассмотрена в [17]. Идентификатор модуля исходного описания, который определяет объект верхнего уровня иерархии при осуществлении процесса поведенческого моделирования, задается в поле выбора значения параметра Simulation top module name.

Для установки требуемых опций поведенческого моделирования, отличающихся от значений параметров, предлагаемых по умолчанию, следует воспользоваться клавишей Options. При ее нажатии открывается диалоговая панель с заголовком Simulation Options, как показано на рис. 3. Открывшаяся диалоговая панель содержит три вкладки — Compilation, Simulation и Advanced, предоставляющие доступ к тем же группам параметров моделирования, что и одноименные вкладки страницы Simulation диалоговой панели Project Settings, рассмотренные ранее. Указав необходимые опции поведенческого моделирования проектируемого устройства или встраиваемой микропроцессорной системы, следует подтвердить их нажатием клавиши OK, расположенной в нижней части диалоговой панели Simulation Options.

Непосредственный запуск процесса поведенческого моделирования осуществляется с помощью клавиши Launch, находящейся в нижней части диалоговой панели Launch Behavioral Simulation. При нажатии данной клавиши автоматически создается соответствующий командный файл для выбранных средств верификации разрабатываемого устройства или встраиваемой системы, содержимое которого генерируется с учетом установленных значений параметров рассматриваемого этапа моделирования. Затем открывается основное окно используемых средств моделирования, и автоматически осуществляется исполнение директив сформированного командного файла. При этом выполняется компиляция исходных модулей описания и всех библиотек, необходимых для моделирования проектируемого устройства или микропроцессорной системы. Дальнейшее рассмотрение этапов моделирования, поддерживаемых интегрированной средой разработки PlanAhead, происходит на примере использования встроенных средств верификации САПР серии Xilinx ISE Design Suite, пользовательский интерфейс которых подробно описан в [15]. Вид основного окна средств моделирования Xilinx ISIM при выполнении этапа поведенческого моделирования разрабатываемых устройств или встраиваемых систем представлен на рис. 4.

На соответствующей вкладке рабочей области открывшегося окна встроенных средств верификации САПР серии Xilinx ISE Design Suite первоначально отображаются временные диаграммы сигналов интерфейсных портов модуля верхнего уровня иерархии HDL-описания проектируемого устройства или встраиваемой микропроцессорной системы, идентификатор которого был указан в поле выбора значения параметра Simulation top module name, представленном в диалоговой панели Simulation Options. Приведенные временные диаграммы сигналов формируются в процессе автоматического выполнения директив командного файла средствами Xilinx ISIM, сгенерированного интегрированной средой разработки PlanAhead для этапа поведенческого моделирования. Длительность представленных временных диаграмм определяется значением параметра Simulation Run Time, которое указано в соответствующем поле редактирования, расположенном на вкладке Simulation диалоговой панели опций моделирования [17]. При необходимости процесс поведенческого моделирования может быть продолжен. Для этого рекомендуется задать требуемую длительность дополнительного интервала моделирования в поле выбора/редактирования, находящемся на оперативной панели основного окна средств Xilinx ISIM справа от кнопок управления моделированием. Чтобы продолжить процесс моделирования в течение указанного периода, следует воспользоваться кнопкой ![]() или командой Run, представленной во всплывающем меню Simulation. Для осуществления процесса моделирования на протяжении всего интервала времени, заданного в тестовом модуле проекта, следует использовать кнопку быстрого доступа

или командой Run, представленной во всплывающем меню Simulation. Для осуществления процесса моделирования на протяжении всего интервала времени, заданного в тестовом модуле проекта, следует использовать кнопку быстрого доступа ![]() или команду Run All из всплывающего меню Simulation. Возможность принудительного прерывания запущенного процесса моделирования обеспечивает кнопка

или команду Run All из всплывающего меню Simulation. Возможность принудительного прерывания запущенного процесса моделирования обеспечивает кнопка ![]() и команда Break.

и команда Break.

При несоответствии полученных результатов поведенческого моделирования ожидаемым временным диаграммам сигналов интерфейсных портов для поиска возможных логических ошибок, допущенных при создании модулей исходного описания проектируемого устройства или аппаратной части встраиваемой микропроцессорной системы, рекомендуется выполнить отладку HDL-кода, содержащегося в этих модулях. В процессе отладки, как правило, кроме отображения информации о состоянии сигналов входных, выходных и двунаправленных портов модуля верхнего уровня иерархии, необходимо проследить поведение отдельных внутренних сигналов модулей исходного описания различного уровня. Чтобы добавить необходимые внутренние сигналы на вкладку временных диаграмм, нужно на вкладке Instances and Processes панели обозревателя иерархической структуры моделируемого устройства или встраиваемой системы выделить соответствующий экземпляр компонента или процесс, после чего в панели объектов Objects поместить указатель на идентификатор требуемого сигнала и нажать левую кнопку мыши. Затем, не отпуская нажатую кнопку, необходимо переместить указатель с выделенным идентификатором в колонку Name вкладки временных диаграмм сигналов и отпустить левую кнопку мыши (рис. 5). Таким образом поочередно перетаскиваются идентификаторы тех внутренних сигналов, чье состояние необходимо контролировать в процессе отладки разрабатываемого устройства или микропроцессорной системы. Кроме того, поддерживается возможность группового выделения нескольких идентификаторов сигналов и одновременного их перемещения на вкладку временных диаграмм. Внутренние сигналы, выделенные в панели объектов Objects, можно также добавить на указанную вкладку с помощью команды Add to Wave Window из контекстно зависимого всплывающего меню, появляющегося после щелчка правой кнопки мыши на строке с идентификатором выбранного сигнала.

При этом следует обратить внимание на то, что временные диаграммы добавленных внутренних сигналов будут формироваться только с того момента процесса моделирования, после которого их идентификаторы были включены в список отображаемых сигналов. Чтобы получить информацию о поведении указанных сигналов в предшествующие временные интервалы моделирования, следует выполнить сброс системы в исходное состояние и повторно запустить процесс моделирования. Сброс результатов моделирования и возврат системы в начальное состояние осуществляется командой Restart из всплывающего меню Simulation или кнопкой быстрого доступа ![]() , расположенной на оперативной панели управления основного окна средств Xilinx ISIM.

, расположенной на оперативной панели управления основного окна средств Xilinx ISIM.

Для повышения информативности процесса отладки HDL-описания разрабатываемого устройства или встраиваемой микропроцессорной системы целесообразно использовать пошаговый режим моделирования. Переход в указанный режим может осуществляться после приостановки процесса моделирования (например, после завершения автоматического исполнения командного файла) или сброса результатов моделирования и возврата системы в начальное состояние. Пошаговый режим моделирования реализуется командой Step из всплывающего меню Simulation или кнопкой быстрого доступа ![]() (рис. 6). Каждое нажатие данной кнопки или однократный выбор указанной команды запускает процесс моделирования исполнения одной (текущей) строки HDL-кода. При этом в окне временных диаграмм сигналов автоматически добавляется соответствующий фрагмент и открывается окно интегрированного HDL-редактора, в котором отображается текст модуля исходного описания моделируемого устройства или микропроцессорной системы, содержащего исполняемую строку кода. В открывшемся окне текущая исполняемая строка HDL-кода отмечена маркером

(рис. 6). Каждое нажатие данной кнопки или однократный выбор указанной команды запускает процесс моделирования исполнения одной (текущей) строки HDL-кода. При этом в окне временных диаграмм сигналов автоматически добавляется соответствующий фрагмент и открывается окно интегрированного HDL-редактора, в котором отображается текст модуля исходного описания моделируемого устройства или микропроцессорной системы, содержащего исполняемую строку кода. В открывшемся окне текущая исполняемая строка HDL-кода отмечена маркером ![]() . Если описание проектируемого устройства или аппаратной части встраиваемой системы имеет иерархическую структуру, каждый уровень которой представлен отдельным файлом, то в процессе пошаговой отладки автоматически открывается несколько рабочих окон встроенного HDL-редактора. Для одновременного контроля сквозного выполнения HDL-кода на всех уровнях иерархии рекомендуется расположить эти окна таким образом, чтобы они не закрывали окно временных диаграмм сигналов, например, как показано на рис. 6.

. Если описание проектируемого устройства или аппаратной части встраиваемой системы имеет иерархическую структуру, каждый уровень которой представлен отдельным файлом, то в процессе пошаговой отладки автоматически открывается несколько рабочих окон встроенного HDL-редактора. Для одновременного контроля сквозного выполнения HDL-кода на всех уровнях иерархии рекомендуется расположить эти окна таким образом, чтобы они не закрывали окно временных диаграмм сигналов, например, как показано на рис. 6.

При отладке модулей исходного описания разрабатываемого устройства или аппаратной части встраиваемой системы, содержащих большой объем HDL-кода, пошаговое моделирование требует солидных временных затрат. Чтобы сократить суммарное время отладки таких модулей, целесообразно задать точки останова (Breakpoint) в процессе моделирования. Для установки контрольных точек необходимо открыть соответствующий файл исходного описания в окне интегрированного текстового редактора, воспользовавшись вкладкой Source Files панели обозревателя иерархической структуры проекта моделируемого устройства или микропроцессорной системы. Затем нужно расположить указатель мыши на требуемой строке HDL-кода и нажать кнопку быстрого доступа ![]() на дополнительной панели инструментов интегрированного текстового редактора или выполнить команду Toggle Breakpoint из контекстно зависимого всплывающего меню, вызываемого щелчком правой кнопки мыши. Аналогичная команда представлена также в выпадающем меню Breakpoint, доступ к которому предоставляет пункт View главного меню средств моделирования Xilinx ISIM. После выполнения указанных действий в выбранной строке HDL-кода появляется пиктограмма

на дополнительной панели инструментов интегрированного текстового редактора или выполнить команду Toggle Breakpoint из контекстно зависимого всплывающего меню, вызываемого щелчком правой кнопки мыши. Аналогичная команда представлена также в выпадающем меню Breakpoint, доступ к которому предоставляет пункт View главного меню средств моделирования Xilinx ISIM. После выполнения указанных действий в выбранной строке HDL-кода появляется пиктограмма ![]() , а информация об установленной контрольной точке автоматически появляется на вкладке Breakpoints консольной панели (рис. 7).

, а информация об установленной контрольной точке автоматически появляется на вкладке Breakpoints консольной панели (рис. 7).

Удаление установленной точки прерывания осуществляется повторным нажатием кнопки ![]() или с помощью команды Toggle Breakpoint при расположении курсора на строке, содержащей пиктограмму

или с помощью команды Toggle Breakpoint при расположении курсора на строке, содержащей пиктограмму ![]() . Возможность одновременного удаления всех зафиксированных контрольных точек предоставляет кнопка

. Возможность одновременного удаления всех зафиксированных контрольных точек предоставляет кнопка ![]() , находящаяся на дополнительной панели инструментов HDL-редактора и на вкладке Breakpoints консольной панели, а также команда Delete All Breakpoints из всплывающего меню Breakpoint. После установки контрольных точек во всех необходимых файлах исходного описания можно продолжить процесс моделирования в непрерывном или пошаговом режиме с текущего момента времени или запустить его заново, выполнив сброс системы моделирования кнопкой

, находящаяся на дополнительной панели инструментов HDL-редактора и на вкладке Breakpoints консольной панели, а также команда Delete All Breakpoints из всплывающего меню Breakpoint. После установки контрольных точек во всех необходимых файлах исходного описания можно продолжить процесс моделирования в непрерывном или пошаговом режиме с текущего момента времени или запустить его заново, выполнив сброс системы моделирования кнопкой ![]() или командой Restart из всплывающего меню Simulation. Повторный запуск процесса моделирования разрабатываемого устройства или встраиваемой микропроцессорной системы в непрерывном режиме осуществляется с помощью кнопок

или командой Restart из всплывающего меню Simulation. Повторный запуск процесса моделирования разрабатываемого устройства или встраиваемой микропроцессорной системы в непрерывном режиме осуществляется с помощью кнопок ![]() и

и ![]() или команд Run и Run All. Выполнение процесса моделирования автоматически приостанавливается при достижении очередной контрольной точки. При этом в окне встроенного HDL-редактора в строке с достигнутой точкой останова отображается маркер

или команд Run и Run All. Выполнение процесса моделирования автоматически приостанавливается при достижении очередной контрольной точки. При этом в окне встроенного HDL-редактора в строке с достигнутой точкой останова отображается маркер ![]() , а в окне временных диаграмм — фрагмент временных диаграмм сигналов, конечное время моделирования которого соответствует текущей контрольной точке.

, а в окне временных диаграмм — фрагмент временных диаграмм сигналов, конечное время моделирования которого соответствует текущей контрольной точке.

После обнаружения в процессе отладки причин некорректных результатов моделирования следует внести изменения в текст исходного описания проектируемого устройства или аппаратной части встраиваемой системы, а затем повторить этап поведенческой верификации проекта. Повторный запуск сеанса моделирования с автоматической компиляцией модулей исходного описания и используемых библиотек осуществляется кнопкой быстрого доступа ![]() или командой Re-launch из всплывающего меню Simulation. Если временные диаграммы, сформированные в процессе поведенческого моделирования, соответствуют требуемому поведению сигналов разрабатываемого устройства или микропроцессорной системы, то можно перейти к выполнению дальнейших этапов проектирования, в том числе к полному временному моделированию.

или командой Re-launch из всплывающего меню Simulation. Если временные диаграммы, сформированные в процессе поведенческого моделирования, соответствуют требуемому поведению сигналов разрабатываемого устройства или микропроцессорной системы, то можно перейти к выполнению дальнейших этапов проектирования, в том числе к полному временному моделированию.

Выполнение этапа полного временного моделирования проектируемого устройства или встраиваемой микропроцессорной системы

Прежде чем приступить к полному временному моделированию разрабатываемого устройства или встраиваемой микропроцессорной системы, необходимо последовательно выполнить этапы синтеза и реализации проекта в кристалле программируемой логики или расширяемой вычислительной платформы. Перед реализацией каждого из этих этапов рекомендуется установить требуемые значения соответствующих параметров.

Для того чтобы указать значения параметров синтеза проектируемого устройства или аппаратной части микропроцессорной системы, следует открыть страницу Synthesis диалоговой панели Project Settings. Для этого нужно воспользоваться командой Synthesis Settings, представленной во всплывающем меню Flow и в разделе Synthesis панели управления основными процессами, выполняемыми в ходе проектирования, Flow Navigator, как показано на рис. 8. На странице Synthesis диалоговой панели Project Settings в поле выбора значения параметра Default Constraint Set следует определить набор временных и топологических ограничений, используемый по умолчанию на этапе синтеза, а в поле выбора значения параметра Strategy — стратегию этого процесса. Подробное описание предопределенных стратегий синтеза и реализации проекта в кристалле, процедуры создания собственных стратегий, а также модулей временных и топологических ограничений выходит за рамки настоящей статьи, поэтому далее приводится только краткая информация о запуске указанных процессов и анализе полученных результатов.

Непосредственный запуск процесса синтеза разрабатываемого устройства или аппаратной части встраиваемой системы производится с помощью команды Run Synthesis, доступ к которой предоставляет всплывающее меню Flow и раздел Synthesis панели управления Flow Navigator (рис. 9). Кроме того, активизация процесса синтеза может осуществляться нажатием кнопки быстрого доступа ![]() , расположенной на оперативной панели управления основного окна интегрированной среды разработки PlanAhead.

, расположенной на оперативной панели управления основного окна интегрированной среды разработки PlanAhead.

При успешном завершении этапа синтеза на экран выводится диалоговая панель с заголовком Synthesis Completed, как демонстрирует рис. 9. Эта диалоговая панель содержит три кнопки с зависимой фиксацией, которые предоставляют возможность выбора следующего этапа процесса проектирования. Если все параметры процесса реализации проекта в кристалле заранее определены, то можно сразу перейти к выполнению этого этапа, зафиксировав в нажатом состоянии кнопку Implement и подтвердив сделанный выбор, воспользовавшись клавишей OK, представленной в нижней части диалоговой панели Synthesis Completed. В противном случае следует отказаться от предлагаемых вариантов нажатием клавиши Cancel и установить требуемые параметры процесса реализации.

Для того чтобы указать набор временных и топологических ограничений и стратегию реализации проекта в кристалле, нужно воспользоваться страницей Implementation диалоговой панели параметров проекта Project Settings. Открыть страницу можно командой Implementation Settings, представленной в разделе Implementation панели Flow Navigator и всплывающем меню Flow (рис. 10).

Для непосредственной активизации процесса реализации проектируемого устройства или аппаратной части встраиваемой системы в кристалле программируемой логики или расширяемой вычислительной платформы следует воспользоваться командой Run Implementation, которая содержится во всплывающем меню Flow и разделе Implementation панели управления Flow Navigator (рис. 11). Запуск рассматриваемого процесса может производиться также нажатием кнопки быстрого доступа ![]() , находящейся на оперативной панели управления основного окна средств проектирования PlanAhead.

, находящейся на оперативной панели управления основного окна средств проектирования PlanAhead.

В случае успешного окончания этапа реализации проектируемого устройства или аппаратной части микропроцессорной системы в кристалле на экране появляется диалоговая панель с заголовком Implementation Completed, чей вид приведен на рис. 11. Открывшаяся диалоговая панель позволяет выбрать последующий этап процесса проектирования с помощью группы кнопок с зависимой фиксацией. Чтобы перейти к этапу полного временного моделирования разрабатываемого устройства или встраиваемой системы, нужно открыть реализованный в кристалле проект. Для этого следует зафиксировать в нажатом состоянии кнопку Open Implemented Design, после чего воспользоваться клавишей OK, расположенной в нижней части диалоговой панели Implementation Completed. Кроме того, открыть проект, реализованный в кристалле, можно с помощью команды Open Implemented Design. Она становится доступной во всплывающем меню Flow и разделе Implementation панели управления Flow Navigator. В результате выполнения указанных действий в рабочей области основного окна интегрированной среды разработки PlanAhead открывается новая вкладка с названием Device, а в панели управления основными процессами, выполняемыми в ходе проектирования, Flow Navigator раскрывается раздел Implemented Design, как показано на рис. 12.

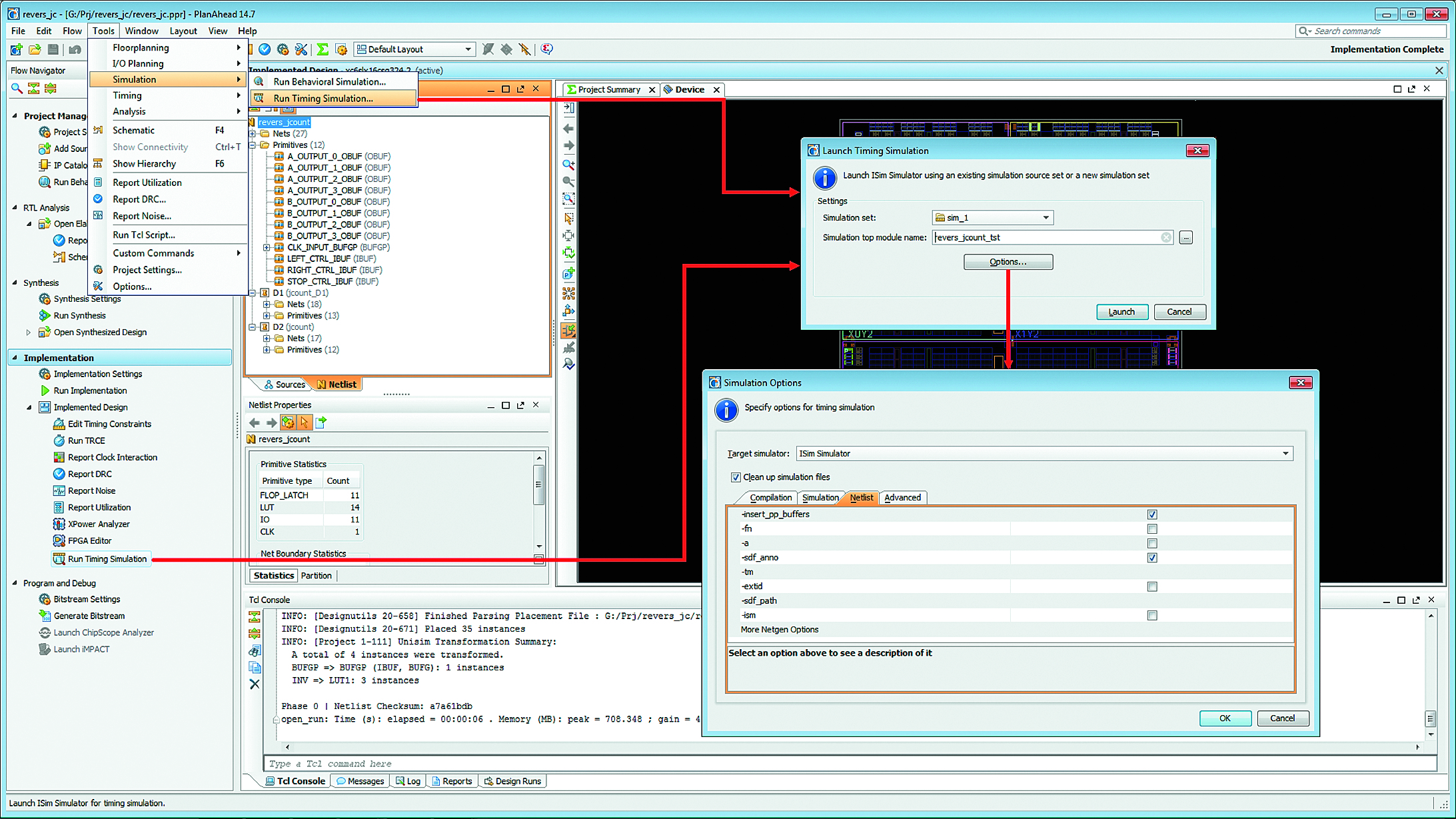

На вкладке Device отображается топологическая структура кристалла, выбранного для реализации разрабатываемого устройства или встраиваемой микропроцессорной системы, в которой в наглядной форме представлены результаты размещения и трассировки проекта. В разделе Implemented Design панели управления Flow Navigator становится доступным ряд команд, предоставляющих возможность выполнения различных операций в процессе проектирования. В частности, здесь представлена команда запуска процесса полного временного моделирования Run Timing Simulation, дублирующая аналогичную команду всплывающего меню Simulation, доступ к которому открывает одноименная строка всплывающего меню Tools (рис. 12). После выбора указанной команды на экран выводится диалоговая панель с заголовком Launch Timing Simulation, чей вид изображен на рис. 12. Эта диалоговая панель предоставляет возможность выбора объекта верхнего уровня иерархии и комплекта тестовых модулей для выполнения этапа полного временного моделирования, а также определения опций этого процесса, которые отличаются от параметров, предлагаемых по умолчанию. Требуемый набор тестовых модулей проекта и идентификатор модуля верхнего уровня иерархии для проведения рассматриваемого этапа определяются таким же образом, как и при осуществлении процесса поведенческого моделирования. Чтобы установить необходимые значения параметров полного временного моделирования, нужно нажать клавишу Options, после чего появляется диалоговая панель с заголовком Simulation Options, как демонстрирует рис. 12. В отличие от процесса поведенческой верификации открывшаяся диалоговая панель параметров полного временного моделирования содержит четыре вкладки — Compilation, Simulation, Netlist и Advanced. Перечисленные вкладки включают те же группы параметров моделирования, что и одноименные вкладки страницы Simulation диалоговой панели Project Settings, представленные выше. После установки требуемых значений параметров полного временного моделирования и подтверждения их нажатием клавиши OK, находящейся в нижней части диалоговой панели Simulation Options, можно приступить к выполнению рассматриваемого этапа верификации проектируемого устройства или встраиваемой микропроцессорной системы.

Для запуска процесса полного временного моделирования нужно воспользоваться клавишей Launch, расположенной в нижней части диалоговой панели Launch Timing Simulation. При нажатии данной клавиши автоматически формируются все необходимые файлы для используемых средств верификации разрабатываемого устройства или встраиваемой системы. Затем на экране появляется основное окно применяемых средств верификации, в котором отображаются временные диаграммы сигналов, сформированные в ходе выполнения полного временного моделирования, осуществляемого при исполнении директив сгенерированного командного файла. Следует обратить внимание на то, что интегрированная среда разработки PlanAhead, в отличие от управляющей оболочки САПР Xilinx ISE Design Suite навигатора проекта, поддерживает одновременный запуск нескольких экземпляров выбранных средств верификации. Таким образом, разработчику предоставляется возможность наглядного сопоставления временных диаграмм сигналов, сформированных в результате поведенческого и полного временного моделирования.

Если в проекте правильно учтены все временные факторы (выбран кристалл с необходимым быстродействием, заданы и выполнены соответствующие ограничения) и рекомендации фирмы Xilinx по формированию и распределению тактовых сигналов, то результаты полного временного моделирования отличаются от итогов функциональной верификации только наличием задержек между входными и выходными сигналами. Для измерения временных параметров сигналов (длительности, задержек) на диаграммах, полученных в результате полного моделирования разрабатываемого устройства средствами Xilinx ISIM, следует расположить основной курсор вкладки временных диаграмм сигналов в начальной или конечной точке измеряемого временного интервала, переместив его с помощью мыши. Затем нужно активизировать дополнительный курсор, поместив указатель мыши в конечную или начальную точку измеряемого интервала и щелкнув левой кнопкой при нажатой клавише Shift на клавиатуре. Основной курсор отображается на экране в виде пунктирной вертикальной линии, а вспомогательный — в виде сплошной (рис. 13). Для точной привязки положения курсора к фронту или спаду выбранного сигнала следует зафиксировать в нажатом состоянии кнопку ![]() , расположенную на дополнительной панели инструментов вкладки временных диаграмм. При активизации дополнительного курсора в нижней части этой вкладки появляется вспомогательная (относительная) шкала времени моделирования, нулевой отсчет которой совпадает с положением основного курсора. Под этой шкалой отображается информация о расположении каждого курсора на основной (абсолютной) временной шкале, а также о длительности измеряемого временного интервала, зафиксированного между курсорами. Эта информация дублирует соответствующие значения, отображаемые рядом с курсорами.

, расположенную на дополнительной панели инструментов вкладки временных диаграмм. При активизации дополнительного курсора в нижней части этой вкладки появляется вспомогательная (относительная) шкала времени моделирования, нулевой отсчет которой совпадает с положением основного курсора. Под этой шкалой отображается информация о расположении каждого курсора на основной (абсолютной) временной шкале, а также о длительности измеряемого временного интервала, зафиксированного между курсорами. Эта информация дублирует соответствующие значения, отображаемые рядом с курсорами.

Чтобы одновременно получить информацию о значениях нескольких временных параметров сигналов, сформированных в процессе моделирования, нужно использовать специальные маркеры, располагая их в требуемых точках временных диаграмм и фиксируя соответствующие интервалы. Установка нового маркера выполняется нажатием кнопки ![]() , представленной на оперативной панели управления и дополнительной панели инструментов вкладки временных диаграмм. Эта кнопка дублирует команду Add Marker из всплывающего меню Markers, доступ к которому открывается при выборе пункта Edit главного меню, при расположении указателя мыши в нужной точке временных диаграмм. Для изменения положения установленного маркера надо поместить курсор на его изображение и нажать левую кнопку мыши. Затем, не отпуская нажатую кнопку, следует переместить маркер в необходимую точку временных диаграмм. Новое положение маркера фиксируется при освобождении левой кнопки мыши. В верхней части каждого установленного маркера отображается координата его положения на основной (абсолютной) временной шкале вкладки временных диаграмм сигналов. При установке двух и более маркеров в нижней части окна автоматически появляется дополнительная (относительная) временная шкала, нулевой отсчет которой совпадает с текущим выделенным маркером. В нижней части каждого маркера представлена координата его положения на дополнительной временной шкале. Таким образом отображается информация о длительности временных интервалов, отделяющих маркеры от текущего выделенного маркера. Для привязки дополнительной временной шкалы к другому маркеру достаточно поместить курсор на изображение этого маркера и щелкнуть левой кнопкой мыши.

, представленной на оперативной панели управления и дополнительной панели инструментов вкладки временных диаграмм. Эта кнопка дублирует команду Add Marker из всплывающего меню Markers, доступ к которому открывается при выборе пункта Edit главного меню, при расположении указателя мыши в нужной точке временных диаграмм. Для изменения положения установленного маркера надо поместить курсор на его изображение и нажать левую кнопку мыши. Затем, не отпуская нажатую кнопку, следует переместить маркер в необходимую точку временных диаграмм. Новое положение маркера фиксируется при освобождении левой кнопки мыши. В верхней части каждого установленного маркера отображается координата его положения на основной (абсолютной) временной шкале вкладки временных диаграмм сигналов. При установке двух и более маркеров в нижней части окна автоматически появляется дополнительная (относительная) временная шкала, нулевой отсчет которой совпадает с текущим выделенным маркером. В нижней части каждого маркера представлена координата его положения на дополнительной временной шкале. Таким образом отображается информация о длительности временных интервалов, отделяющих маркеры от текущего выделенного маркера. Для привязки дополнительной временной шкалы к другому маркеру достаточно поместить курсор на изображение этого маркера и щелкнуть левой кнопкой мыши.

Если полученные результаты временного моделирования не удовлетворяют предъявляемым требованиям, то следует проанализировать выполнение временных и топологических ограничений, установленных в проекте. Кроме того, рекомендуется обратить внимание на стратегии, используемые на этапах синтеза и реализации проекта в кристалле. При необходимости нужно изменить ограничения проекта и/или выбрать другие стратегии процессов синтеза и реализации. Для оперативной корректировки модулей ограничений проекта можно воспользоваться командой Edit Timing Constraints, представленной в разделах Synthesis и Implementation панели управления Flow Navigator. После выбора указанной команды в области расположения рабочих окон интегрированной среды разработки PlanAhead добавляется вкладка с названием Timing Constraints (UCF), как показано на рис. 14. Она предоставляет быстрый доступ к различным группам временных ограничений проекта.

После корректировки установленных ограничений нужно повторить все необходимые этапы проектирования. Средства разработки PlanAhead предоставляют возможность запуска нескольких вариантов процессов синтеза и реализации с различными комбинациями временных ограничений и стратегий этих процессов. Последующий анализ полученных результатов позволяет выбрать оптимальный вариант реализации проекта в кристалле, для верификации которого следует повторить этап полного временного моделирования.

- Кузелин М. О., Кнышев Д. А., Зотов В. Ю. Современные семейства ПЛИС фирмы Xilinx. Справочное пособие. М.: Горячая линия – Телеком, 2004.

- Зотов В. Особенности архитектуры нового поколения ПЛИС с архитектурой FPGA фирмы Xilinx // Компоненты и технологии. 2010. № 12.

- Зотов В. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPack ISE. М.: Горячая линия – Телеком, 2003.

- Зотов В. Проектирование встраиваемых микропроцессорных систем на базе расширяемых процессорных платформ семейства Zynq‑7000 AP SoC в САПР Xilinx ISE Design Suite // Компоненты и технологии. 2012. № 4. 2014. № 4. 2015. № 1.

- Зотов В. Расширение семейства программируемых систем на кристалле Zynq‑7000 AP SoC // Компоненты и технологии. 2013. № 12. 2014. № 1.

- Zynq‑7000 All Programmable SoC Overview. Advance Product Specification. Xilinx, 2013.

- Zynq‑7000 All Programmable SoC (XC7Z010, XC7Z015, and XC7Z020): DC and AC Switching Characteristics. Xilinx, 2013.

- Zynq‑7000 All Programmable SoC (XC7Z030, XC7Z045, and XC7Z100): DC and AC Switching Characteristics. Xilinx, 2013.

- Zynq‑7000 All Programmable SoC Technical Reference Manual. Xilinx, 2013.

- Zynq‑7000 All Programmable SoC: Concepts, Tools, and Techniques (CTT) A Hands-On Guide to Effective Embedded System Design. Xilinx, 2013.

- Zynq‑7000 All Programmable SoC Software Developers Guide. Xilinx, 2013.

- Zynq‑7000 All Programmable SoC PCB Design and Pin Planning Guide. Xilinx, 2013.

- 7 Series FPGAs and Zynq‑7000 All Programmable SoC XADC Dual 12‑Bit 1 MSPS Analog-to-Digital Converter User Guide. Xilinx, 2012.

- Зотов В. Средства автоматизированного проектирования и этапы разработки встраиваемых микропроцессорных систем на базе расширяемых процессорных платформ семейства Zynq‑7000 AP SoC // Компоненты и технологии. 2014. № 2–3.

- Зотов В. Моделирование цифровых устройств, проектируемых на основе ПЛИС фирмы Xilinx, средствами ISIM в САПР ISE Design Suite // Компоненты и технологии. 2013. № 2–3.

- Зотов В. ModelSim — система HDL-моделирования цифровых устройств // Компоненты и технологии. 2002. № 6.

- Зотов В. Моделирование цифровых устройств и встраиваемых микропроцессорных систем, проектируемых на основе ПЛИС фирмы Xilinx в интегрированной среде разработки PlanAhead. Часть 1 // Компоненты и технологии. 2016. № 1.

4 августа, 2020

4 августа, 2020 29 мая, 2020

29 мая, 2020 11 января, 2021

11 января, 2021