Libero SoC — быстрый старт

Обычно разработчики, долгое время работающие с ПЛИС какой-то одной компании, неохотно принимают необходимость осваивать ПЛИС других фирм. В первую очередь, это происходит из-за огромного объема информации, который следует воспринять: нужно научиться работать с незнакомой САПР, изучить архитектурные особенности микросхем, пройти неизбежные «подводные камни» и многое другое. Времени при этом будет потрачено немало, поэтому для такой работы нужны серьезные основания.

Оснований для того, чтобы начать освоение ПЛИС фирмы Microsemi [1], вполне достаточно из-за их уникальных особенностей. Наиболее известен, наверное, широкий ассортимент радиационно-стойких ПЛИС, который перешел к Microsemi вместе с фирмой Actel. Некоторые производители публикуют положительные результаты радиационных испытаний отдельных экземпляров своих ПЛИС, никак не отражая эти результаты в спецификациях. В отличие от них, компания Microsemi параметры радиационной стойкости приводит в справочных данных, гарантируя тем самым надежную работу микросхем в условиях воздействия радиации. Кроме того, фирма выпускает очень интересные системы на кристалле (SoC), ПЛИС с ультранизким потреблением, а также несколько семейств однократно программируемых ПЛИС, которые могут быть востребованы в разных областях применения.

В этой статье на учебном примере показан маршрут проектирования в среде Libero SoC компании Microsemi. Статья предназначена для специалистов, уже имеющих опыт работы с ПЛИС, поэтому основные понятия здесь не затрагиваются. Если эта статья кому-то поможет сэкономить несколько дней, автор сочтет свою задачу выполненной.

Установка ПО Libero SoC

Самый первый шаг — конечно же, получение дистрибутива пакета Libero SoC и установка его на рабочем месте. Дистрибутив без всяких ограничений и бесплатно можно получить на сайте фирмы Microsemi. Для этого с главной страницы сайта [1] нужно перейти в раздел ASIC, FPGA & SoC. (Здесь и далее мы будем по возможности избегать прямых ссылок, так как на сайте Microsemi часто происходят изменения, и к моменту публикации статьи прямые ссылки могут не работать.) В этот же раздел ведет хорошо известная, «традиционная» ссылка www.actel.com. Здесь находим ссылку Libero SoC Design Software, проходим по ней и щелкаем по ссылке Downloads. Пройти дальше без регистрации нельзя, но регистрация бесплатная, и ее достаточно выполнить только один раз. Далее будет предложено два варианта загрузки.

Первый вариант загрузки

Download Libero SoC v11.1 (Windows) (small EXE, Web Install) — скачать специальную программу-инсталлятор, которая после диалога с пользователем загрузит на его компьютер только выбранные компоненты. Это очень полезная возможность, так как полный объем дистрибутива заметно превышает гигабайт. После загрузки и запуска инсталлятор предложит выбор: установить пакет Libero SoC вместе с синтезатором Synplifyфирмы Synopsys и системой моделирования Modelsim фирмы Mentor Graphics или же загрузить только Libero SoCSA (Standalone). Если у вас оба упомянутых пакета уже установлены, и вы уверены, что легко сможете добиться их совместной работы с Libero SoC, то можно сэкономить время и выбрать Standalone. Далее инсталлятор предложит принять лицензионное соглашение, а затем появится окно Select Features (рис. 1), в котором можно выбрать требуемые компоненты.

Отметим, что в этом окне предлагается выбрать поддержку далеко не всех семейств ПЛИС, выпускаемых фирмой Microsemi. Дело в том, что среда Libero SoC предназначена для работы с новыми семействами микросхем. Эта среда продолжает развиваться, регулярно выходят ее новые версии. Для работы с более ранними семействами, которых нет в списке из нашего окна, предназначена другая версия ПО, которая называется Libero IDE. Ее также можно скачать без всяких ограничений, но искать ее на сайте Microsemi следует отдельно. Путь к ней время от времени меняется, поэтому лучше всего воспользоваться поиском на сайте по ключевым словам Libero IDE.

После выбора нужных компонентов нажимаем на кнопку Next, инсталлятор предложит проверить параметры установки. Далее нажимаем кнопку Install, и теперь установка пойдет без нашего участия.

Второй вариант загрузки

Download Libero SoC v11.1 (Windows) (large EXE, using Download Manager) — здесь предлагается скачать полный дистрибутив пакета. Этот вариант может оказаться удобнее, если предполагается установить Libero SoC сразу на несколько компьютеров. Кроме того, инсталлятор, предлагаемый в первом варианте, не способен продолжить работу после перезагрузки компьютера, и, если скорость соединения с Интернетом не позволяет закончить установку за день, то на следующий день придется начинать работу сначала. И еще одно важное соображение. Ваш сложный проект, который работал после компиляции в прежней версии Libero SoC, может по какой-то причине перестать работать после компиляции в новой версии. Часто сжатые сроки не позволяют искать причины этого явления, поэтому полезно иметь архив дистрибутивов предыдущих версий.

На момент написания статьи (сентябрь 2013 года) механизм загрузки полной версии работает через всплывающее окно (pop-up), поэтому нужно разрешить браузеру открыть это окно. В окне предлагается установить фирменный менеджер загрузок от Microsemi (Microsemi Download Manager), который и скачает полный дистрибутив. Однако, скорее всего, у вас на компьютере уже давно есть свой менеджер загрузок, например, бесплатная и очень удобная программа Download Master фирмы Westbyte [2]. Для такого случая, а также на случай возникновения каких-либо проблем со своей программой фирма Microsemi в том же всплывающем окне предлагает прямую ссылку на дистрибутив: download the file without the Microsemi Download Manager.

Пока закачивается дистрибутив, можно заняться получением бесплатной лицензии на использование Libero SoC. Она называется Gold, и ее возможностей более чем достаточно не только для ознакомления, но и для полноценной работы во многих случаях. Для ее получения следует из раздела FPGA & SoC, в котором мы уже побывали, пройти по ссылке Licensing Information и на открывшейся странице щелкнуть по ссылке Request a FREE License or Register a Purchased License. В свою очередь, на появившейся странице Microsemi SoC Licensing будет кнопка Request Free License. Щелкаем по ней, выбираем ссылку Libero Gold Node Locked for Windows. Здесь нам предложат ввести серийный номер тома раздела жесткого диска (Disk ID). Обратите внимание на то, что нужно ввести серийный номер раздела C:, даже если вы планируете установить Libero SoC в другой раздел. На всякий случай, вот краткая инструкция по получению серийного номера тома:

- Для Windows XP: «Пуск»→«Выполнить».

Для Windows 7: «Пуск»→«Все программы»→«Стандартные»→«Выполнить».

- Далее в открывшемся окне ввести CMD и нажать OK.

- В открывшемся черном окне посмотреть, с чего начинается последняя строка. Если она начинается с C:\, то нужно ввести команду DIR и нажать клавишу Enter. Если же последняя строка почему-либо начинается с D:\ или с какого-либо другого имени тома, то надо ввести C:\, нажать Enter и только после этого ввести команду DIR и нажать Enter.

- Скорее всего, в ответ на команду DIR вы получите много строк, и начало вашего диалога уйдет под верхнюю границу окна. Поднимите мышью скроллер в правой части окна вверх до упора, и вы найдете строку вида «Серийный номер тома: 048C:DF58» (рис. 2). Два четырехразрядных шестнадцатеричных числа, разделенные дефисом, — это и есть нужный нам номер.

Этот номер следует ввести для получения лицензии и нажать Submit. В ответ сайт сообщит Software ID, например Your Software ID is 33b-283f-75d. Можно сохранить этот ID, так как сайт Libero его запомнит и будет показывать в списке ваших лицензий. Возможно, это когда-нибудь пригодится. Количество лицензий на одного зарегистрированного пользователя, видимо, не ограничивается — автор не сумел найти упоминаний о таком ограничении. Таким образом, один и тот же дистрибутив можно свободно развернуть на нескольких компьютерах.

Вскоре на указанный при регистрации адрес электронной почты придет письмо с лицензионным файлом и подробной инструкцией по установке лицензии. В кратком пересказе эта инструкция выглядит так:

- Создать в корневой папке диска C: папку flexlm.

- Сохранить в этой папке приложенный к письму файл dat.

- Открыть «Панель управления».

- Сделать двойной щелчок мышью по значку «Система».

- Если у вас ОС Windows XP, переключитесь на вкладку «Дополнительно», если Windows 7 — щелкните по ссылке «Дополнительные параметры системы».

- Щелкните по кнопке «Переменные среды».

- Если среди пользовательских переменных уже есть переменная LM_LICENSE_FILE, то выберите ее, нажмите на кнопку «Изменить…» и припишите к ее существующему значению после точки с запятой имя файла лицензии вместе с путем к нему, например C:\flexlm_libero\License.dat.

- Если такой переменной нет, то нажмите на кнопку «Создать…» и создайте такую переменную, аналогично вписав имя файла лицензии с путем в поле значения.

Примечание. Возможно, на диске C: вашего компьютера уже есть папка flexlm, а в ней уже лежит файл license.datот другого программного обеспечения. Папка с файлом лицензии для Libero может быть названа произвольным именем, нужно создать эту папку и ее имя вписать в значение переменной среды.

- Аналогично создайте переменные среды SNPSLMD_LICENSE_FILE и SYNPLCTYD_LICENSE_FILEи присвойте им такое же значение, что и для LM_LICENSE_FILE.

- Закройте последовательно все окна, вызванные из «Панели управления», нажимая на кнопку ОК.

После оформления лицензии можно запускать инсталляцию. Во время нее будет задан вопрос о лицензии. Нужно будет ответить, что она уже есть, и, если все сделано правильно, то инсталлятор сам ее найдет. Все диалоги, появляющиеся при установке полного дистрибутива, не отличаются от диалогов web-инсталлятора. В конце установки будет предложено подключить программатор FlashPro, но это можно будет сделать и позже.

Во время инсталляции может появиться сообщение об ошибке, как показано на рис. 3.

Оно возникает при работе как web-инсталлятора, так и полного дистрибутива. Установка Libero SoC после него прерывается, Libero IDE продолжает устанавливаться, но после установки не работает. На сайте Microsemiесть инструкция по подготовке 64-разрядной ОС Windows XP, но автору эта инструкция помогла установить Libero на 32-разрядную Windows 7. Вот она:

- Из Control Panel (панель управления) открываем раздел Administrative Tools (администрирование).

- Открываем пункт Local Security Policy (локальная политика безопасности).

- Далее открываем Software Restriction Policies (политика ограниченного использования программ).

- Если политики не определены, выбираем в меню пункт Action (действие) и далее Create New Policies(создать новую политику).

- Делаем двойной щелчок мышью по пункту Enforcement (применение) в правой части панели.

- В открывшемся окне выбираем All users except local administrators — применение политики ограниченного использования программ для всех пользователей, кроме локальных администраторов.

После окончания установки Libero SoC следует вернуть эту настройку в исходное состояние — для всех пользователей, иначе в системе могут возникнуть неприятные неожиданности. У автора после перезагрузки перестал запускаться процесс svchost и нарушилась связь с Интернетом.

Первый запуск, создание проекта

Наконец, все установочные хлопоты закончены. Находим в меню «Пуск» группу Microsemi Libero SoC с номером установленной нами версии (сейчас — 11.1), а в ней ярлык Libero SoC, и щелкаем по нему. Через какое-то время весь экран займет серое поле с вопросом “Would you like to check for updates to the Libero software now?” Это, наверное, самая безобидная из трудностей, возникающих при работе с Libero. Скорее всего, в следующих версиях ПО ее не будет. После двойного щелчка по синей полосе в верхней части экрана выясняется, что это неудачно развернувшееся на весь экран небольшое диалоговое окно с предложением обновить ПО прямо сейчас. Появление этого окна можно будет потом отключить в настройках. Отвечаем так, как вам нравится, идем дальше. Перед нами появляется окно среды Libero.

Его правую часть занимает стартовая страница (Start Page). На ней есть много полезных ссылок на различные справочные и обучающие материалы, которыми можно пользоваться во время работы. Наверху мы видим ссылку New, приглашающую нас создать новый проект. Пройдем по ней. Откроется окно New Project(рис. 4).

Названия всех полей в окне говорят сами за себя. Наглядность и понятность представления информации — это одна из сильных сторон Libero, мы еще не раз в этом убедимся. Заполняем нужные поля, жмем ОК. Если потом понадобится что-то изменить, то все эти настройки можно будет найти в меню Project/Settings.

Теперь перед нами появилось готовое к работе главное окно среды Libero SoC. Оно разделено на четыре области (рис. 5).

Каждая из этих областей может содержать по несколько окон, одно поверх другого. Переключение между окнами осуществляется при помощи вкладок. Для удобства изложения присвоим областям главного окна имена, показанные на рисунке: левая верхняя, левая нижняя, правая и нижняя. Включать и выключать отображение окон можно через меню View/Windows, оно одно для всех четырех областей.

Начнем с окна Design Flow, которое мы видим в левой нижней области (рис. 6). Оно наглядно отображает ход проектирования. Наверное, для изучения работы в Libero достаточно было бы внимательно рассмотреть это окно сверху вниз, если бы не обилие тонкостей.

Окно имеет иерархическую древовидную структуру. Каждая ветвь дерева — этап работы над проектом. Двойной щелчок мышью по какой-либо строке в окне Design Flow вызывает соответствующее действие: создание нового файла проекта, запуск моделирования, синтез и т. д.

Создание исходных текстов проекта

Первая ветвь в окне Design Flow→Create Design — создание проекта. Исходные файлы — как синтезируемые, так и тестбенчи — можно создавать двумя путями: при помощи интерактивного средства SmartDesign или просто писать их на каком-либо языке описания аппаратуры. Раз уж мы начали работать в Libero, имея за плечами наработки в других САПР ПЛИС, то нам, скорее всего, захочется обеспечить максимальную переносимость между нашими прошлыми, настоящими и будущими проектами. Поэтому начнем создавать новый проект на языке описания аппаратуры. На долю SmartDesign можно оставить аппаратно-зависимые блоки, такие как узлы ФАПЧ (PLL). Заметим, что SmartDesign среди прочего создает и HDL-файлы, к которым можно обращаться из наших исходных текстов.

Итак, начинаем создавать наш учебный проект. Пусть это будет простой четырехразрядный двоичный счетчик. Делаем двойной щелчок мышью по пункту Create HDL ветви Create Design. Появляется диалог создания нового HDL-файла (рис. 7). Предпочтительный язык ввода мы задали при создании проекта (рис. 4), поэтому здесь уже отмечен язык VHDL. Вводим имя проекта counter и оставляем установленным флажок Initialize file with standard template, чтобы Libero сразу предложила нам удобный шаблон для заполнения. Жмем ОК.

В правой области главного окна поверх стартовой страницы появляется окно с шаблоном для нашего будущего проекта. Шаблон удобный, в нем только основное и нужное. К сожалению, не слишком удобен встроенный в среду Libero текстовый редактор. С его ограниченной функциональностью поначалу можно было бы и смириться. Но размер шрифта в нем очень мал, и его изменить невозможно, глаза быстро начинают уставать. Поэтому воспользуемся внешним текстовым редактором. «Путеводитель» по специализированным тестовым редакторам от самых продвинутых профессионалов с подробным обсуждением можно найти в [3]. Автор пользуется редактором Notepad++ [4]. Шаблон с заданным именем сразу после появления автоматически сохраняется на жестком диске, и его можно загружать во внешний редактор.

Для этого осталось найти новый файл у себя на жестком диске. Искать его следует в указанной при создании проекта папке, в ней есть папка с именем проекта (у нас «test01»), а там сейчас уже есть множество вложенных папок. Исходные файлы на языке описания аппаратуры хранятся в папке “HDL”. Идем туда через «Проводник» Windows. Редактор Notepad++ при установке встроил в контекстное меню «Проводник» пункт Edit with Notepad++. Щелкаем по файлу counter.vhd правой клавишей мыши и загружаем его в редактор.

Среда Libero автоматически отслеживает изменения открытых исходных файлов и всегда спрашивает, что делать при обнаружении изменений. Поэтому пользоваться внешним редактором можно без риска «раздвоения» исходных текстов. Если эти вопросы отвлекают, то можно просто временно закрыть редактируемый файл в Libero. Потом его можно будет снова открыть из окна Files в левой верхней части главного окна. А редактор Notepad++ можно настроить так, чтобы он перезагружал измененные извне файлы, не задавая вопросов (меню «Опции/Настройка»→«Разное»→«Автоопределение статуса файлов»: установить флажки «Включить» и «Обновлять не спрашивая»). Таким образом, можно закончить редактирование файла во внешнем редакторе, затем открыть его в Libero, щелкнуть правой мыши по тексту и запустить проверку синтаксиса, выбрав из контекстного меню пункт Check HDL file. После этого небольшие правки можно сделать прямо в Libero, и после сохранения они появятся в Notepad++.

Пусть исходный текст нашего учебного проекта на языке VHDL выглядит так:

library IEEE;

use IEEE.std_logic_1164.all;

use work.functions.all;

entity counter is

port (

clock : in std_logic;

reset : in std_logic;

code : out std_logic_vector(3 downto 0)

);

end counter;

architecture counter_0 of counter is

signal counter4 : natural range 0 to 15;

begin

process(clock,reset)

begin

if reset = '1' then counter4 <= 0;

elsif rising_edge(clock) then

if counter4 = 15 then counter4 <= 0;

else counter4 <= counter4 + 1; end if;

end if;

end process;

code <= NaturaltoSLV(counter4,4);

end counter_0;

Немного прокомментируем этот код. В строке

if reset = '1' then counter4 <= 0;

описывается асинхронный сброс счетчика. Эта строка дает повод упомянуть о том, что на ПЛИС Microsemi из-за их архитектурных особенностей обязательно должен быть заведен сигнал начального сброса, так как в них невозможно при помощи прошивки задать начальное состояние триггеров. Это может показаться неожиданным после работы, например, с ПЛИС фирмы Altera, где в настройках компилятора можно установить флажок NOT Gate Push-Back, и ценой некоторого увеличения занимаемых ресурсов ПЛИС обеспечить заданные состояния триггеров по окончании конфигурации. Компания Microsemi в [5] предлагает интересный вариант: использовать для начального сброса инверсный сигнал готовности модуля PLL. Но, во-первых, не во всех микросхемах есть PLL, а во-вторых, при неудачной разводке печатной платы или при наличии сильных помех такой сброс может происходить самопроизвольно в непредсказуемые моменты.

Триггеры, на которые забыли завести сброс, можно обнаружить при сравнении результатов функционального моделирования (Pre-Synthesized) и моделирования после разводки (Post-Layout). Если при функциональном моделировании выходы триггеров ведут себя так, как ожидалось, а при моделировании после разводки они оказываются в неопределенном состоянии, то дело, скорее всего, именно в том, что в первом случае система моделирования присвоила им какие-то начальные состояния, а во втором — нет.

Теперь посмотрим на строку:

code <= NaturaltoSLV(counter4,4)

Здесь упоминается функция NaturaltoSLV. Она необходима для преобразования кода счетчика, описанного как натуральное число, в данные типа std_logic_vector, которые должны появляться на выходе. Для таких преобразований часто рекомендуют использовать готовые пакеты VHDL, но во многих простых случаях можно вместо изучения этих пакетов быстро написать свои функции и поместить их в свой пакет. В нашем примере используется пакет functions, на который в нашем коде есть ссылка в строке 3. Этот пакет находится в отдельном файле functions.vhd.

Текст функции NaturaltoSLV выглядит так:

function NaturalToSLV (NaturalValue: natural; Size: natural) return std_logic_vector is

variable TempNatural: natural;

variable result : std_logic_vector(Size - 1 downto 0);

begin

TempNatural := NaturalValue;

for i in 0 to Size - 1 loop

if TempNatural rem 2 = 1 then result(i) := '1';

else result(i) := '0'; end if;

TempNatural := TempNatural / 2;

end loop;

return result;

end NaturalToSLV;

Конечно, такой простой код можно было просто вставить в файл с кодом счетчика, но нас сейчас интересует работа с пакетами VHDL в среде Libero. Свои пакеты нужно создавать и сохранять в той папке проекта, где уже лежат файлы на языке описания аппаратуры: папке hdl. Во время работы Libero автоматически создает копии этих пакетов и сохраняет их в папке package. При необходимости внесения изменений в текст пакета следует править тот экземпляр, который лежит в папке hdl.

Создаем файл functions.vhd, сохраняем его в папку hdl нашего проекта. Оба файла открываем в Libero (среда автоматически обнаруживает появление новых файлов и отображает их в окне Files в левой верхней части главного окна) и проверяем их на синтаксические ошибки: щелкаем правой кнопкой мыши в любом месте поля редактора и выбираем из выпавшего меню пункт Check HDL File. Сообщения об ошибках появляются в нижней части главного окна, в окне протокола (Log). В сообщениях есть гиперссылки на места обнаружения ошибок. Отметим, что отсутствие ошибок на этом этапе еще не означает полного отсутствия ошибок в проекте. Новые ошибки могут быть выявлены во время моделирования и синтеза.

И последний штрих: указание корневого файла проекта. Иерархия проекта отображается в окне DesignHierarchy в левой верхней части главного окна. В иерархии нашего проекта всего один файла, counter.vhd. Он и отображается в окне иерархии жирным шрифтом, то есть как корневой. Среда Libero, как правило, сама находит корневой файл, исходя из анализа содержимого файлов. Если ей это почему-то не удалось, или, например, нужно моделировать только часть сложного проекта, то щелкните в окне Design Hierarchy правой кнопкой мыши по нужному файлу и из выпавшего меню выберите пункт Set As Root.

На этом подготовка исходных текстов закончена.

Функциональное моделирование

Далее в окне Design Flow следует функциональное моделирование — пункт Simulate в разделе Verify Pre-Synthesized Design. Договоримся не называть моделирование симуляцией, потому что в русском языке у этого слова уже было другое значение задолго до появления ПЛИС.

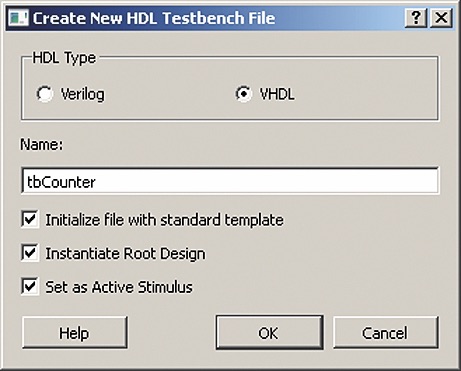

Перед началом моделирования нужно описать входные сигналы, воздействующие на наш проект. Снова для переноса выберем из всех вариантов, предлагаемых Libero SoC, тестбенч на языке HDL. Создание такого тестбенча в Libero автоматизировано, очень наглядно и понятно. Вернемся к разделу Create Design окна DesignFlow и сделаем двойной щелчок мышью по пункту Create HDL Testbench. В ответ появится окно Create NewHDL Testbench File (рис. 8).

В поле Name вводим имя нашего тестбенча, все флажки оставляем установленными. Их назначение следующее:

- Initiatefilewithstandardtemplate — означает, что в новом файле будет присутствовать стандартный шаблон.

- InstantiateRootDesign — тестбенч будет создан для корневого файла нашего проекта.

- SetasActiveStimulus — именно этот тестбенч будет использоваться в ближайшем сеансе моделирования.

Жмем ОК.

Файл будет сохранен в папке Stimulus нашего проекта. Загрузим его оттуда в наш внешний редактор. Уберем для экономии места обильные комментарии, останется интуитивно понятный текст. Вот он:

library ieee;

use ieee.std_logic_1164.all;

entity tbCounter is

end tbCounter;

architecture behavioral of tbCounter is

constant SYSCLK_PERIOD : time := 100 ns;

signal SYSCLK : std_logic := '0';

signal NSYSRESET : std_logic := '0';

component counter

port(

clock : in std_logic;

reset : in std_logic;

code : out std_logic_vector(3 downto 0)

);

end component;

begin

process

variable vhdl_initial : BOOLEAN := TRUE;

begin

if ( vhdl_initial ) then

-- Assert Reset

NSYSRESET <= '0';

wait for ( SYSCLK_PERIOD * 10 );

NSYSRESET <= '1';

wait;

end if;

end process;

-- 10MHz Clock Driver

SYSCLK <= not SYSCLK after (SYSCLK_PERIOD / 2.0 );

-- Instantiate Unit Under Test: counter

counter_0 : counter

-- port map

port map(

clock => SYSCLK,

reset => NSYSRESET,

code => open

);

end behavioral;

Мы видим, что Libero создала тактовый сигнал SYSCLK и сигнал начального сброса NSYSRESET, нашла в нашем проекте тактовый сигнал clock и сигнал сброса reset и правильно подала на них свои сигналы (две первые строчки кода после строки port map). В единственном операторе process формируется сигнал начального сброса отрицательной полярности: вначале низкий уровень, потом через десять периодов тактовой частоты — высокий. Вспомним, что наш счетчик сбрасывается высоким уровнем (if reset = ‘1’ then counter4 <= 0). Переименуем сигнал NSYSRESET в SYSRESET, чтобы не было путаницы, и изменим полярность сигнала начального сброса в тестбенче:

SYSRESET <= '1'; wait for ( SYSCLK_PERIOD * 10 ); SYSRESET <= '0';

Для более сложных проектов можно добавлять неограниченное количество сигналов и описывать их изменения в теле этого оператора process. Строка:

SYSCLK <= not SYSCLK after (SYSCLK_PERIOD / 2.0 )

формирует тактовую частоту 10 МГц. Выходы нашего счетчика никуда не подключены (ключевое слово open).

Теперь подготовим взаимодействие Libero с системой моделирования Modelsim. Сначала найдем в правом верхнем углу окна Design Flow кнопку с изображением гаечного ключа поверх шестеренки. Это кнопка Configure Design Flow Options…. Нажмем на нее. Появится окно Project Settings. Выберем в левом поле этого окна пункт DO File (рис. 9).

Оставляем установленным флажок Use automatic DO file. В поле Simulation runtime вводим время, за которое мы сможем полностью смоделировать работу счетчика, 4 мкс нам хватит. Нажимаем кнопку Save, затем Close.

Теперь щелкаем правой кнопкой мыши по пункту Simulate в разделе Verify Pre-Synthesized Design и из выпавшего меню выбираем Organize Input Files и затем Organize Source Files. Появляется окно, показанное на рис. 10.

Слева вверху мы видим выбранную опцию Libero (default list), которая сообщает, что среда автоматически подготовила список исходных файлов для моделирования. Справа, в списке Assotiated Source Files мы видим файлы, которые будут участвовать в моделировании. Порядок их следования имеет значение: файлы более низкого уровня иерархии должны располагаться выше. В нашем случае все правильно, но иногда Libero ошибается, и тогда нужно заменить опцию Libero (default list) на User и переставлять файлы при помощи двух кнопок со стрелками. Если этого не сделать, то в моделировании будут участвовать не все файлы, и Modelsim будет отмечать их в протоколе словами not bound. Очевидно, что результаты моделирования при этом будут неадекватными. Иногда Modelsim из-за какой-то ошибки воспринимает совершенно правильный порядок в списке как неверный. В этом случае следует заменить опцию Libero (default list) на User, ничего при этом не переставляя, и моделирование пройдет нормально.

Если бы у нас был сложный проект из многих файлов, и некоторые из них не участвовали бы в данном сеансе моделирования, то они отображались бы в левом списке Source files in the project. При необходимости обмен файлов между списками можно делать кнопками Add и Remove.

Разобравшись со списком исходных файлов, нажимаем ОК и переходим к следующему действию — указанию нужного тестбенча. Щелкаем правой кнопкой мыши по пункту Simulate в разделе Verify Pre-Synthesized Design и из выпавшего меню выбираем Organize Input Files, а затем Organize Stimulus Files. Появляется окно, аналогичное показанному на рис. 10. Какие-либо ошибки в нем случаются редко, Libero автоматически справляется с управлением, но проверить надо.

Теперь все готово, и двойным щелчком левой кнопки мыши по пункту Simulate в разделе Verify Pre-Synthesized Design окна Design Flow мы запустим Modelsim. Описание работы в этом пакете выходит за рамки этой статьи. Отметим только один прием работы. Мы устанавливали параметры автоматически формируемого DO-файла (рис. 9), этот файл называется run.do и появляется в папке simulation нашего проекта. По результатам работы этого файла Modelsim отображает только сигналы, описанные в тестбенче. В нашем случае это SYSRESET и SYSCLK. А нам бы очень хотелось посмотреть на выходы счетчика. Сделать это просто: нужно в окне Modelsim найти в поле sim — Default строку counter_0 и щелкнуть по ней мышью. После этого в поле Objects появятся объекты экземпляра счетчика counter_0 из нашего тестбенча. Перетащим объект code (выходы счетчика) в поле Wave и запустим моделирование сначала. Результат работы Modelsim показан на рис. 11.

При каждом новом запуске Modelsim крайне неудобно создавать вручную список отображаемых сигналов, особенно если их много. Поэтому мы сохраним набор этих сигналов в дополнительном DO-файле и передадим информацию о нем в Libero.

Найдем в левом верхнем углу окна Modelsim кнопку с изображением дискеты, она называется Save Format, и щелкнем по ней. Тот же результат можно получить, нажав на клавиши Ctrl+S. Modelsim предложит нам сохранить DO-файл в папке Simulation, но лучше положить этот файл в другое место. Дело в том, что наиболее распространенный выход из ситуации, когда вроде бы все правильно, а моделирование не получается, — это стереть всю папку Simulation. А вместе с ней будут уничтожены и наши DO-файлы. Поэтому присвоим файлу какое-нибудь понятное нам имя, пусть это будет counter.do, и сохраним его, например, в папке Stimulus.

Теперь закроем Modelsim и вернемся в Libero. Снова кнопкой с гаечным ключом вызовем окно ProjectSettings и выберем в левом поле пункт Waveforms. Установим флажок Include DO file, нажмем на кнопку с многоточием и найдем наш файл counter.do. Затем последовательно нажмем на кнопки Save и Close. Если мы теперь снова запустим Modelsim, то он покажет нам все требуемые сигналы.

Задание ограничений

Создание ограничений (constraints) — очень обширная тема. В нашей статье начального уровня мы затронем лишь те, которые нам понадобятся в первую очередь.

Сначала создадим совсем простой файл временных ограничений и укажем в нем нашу тактовую частоту, чтобы ее можно было использовать для временного анализа. Вот все его содержимое:

create_clock -name {counter|clock} -period 100.000000 -waveform {0.000000 5.000000} clock

Сохраним этот файл под именем counter.sdc в папке constraint нашего проекта.

Теперь создадим файл с назначением выводов микросхемы ПЛИС для портов проекта, он будет называться counter.pdc и располагаться в той же папке. Синтаксис этого файла проще показать, чем описать:

#set_io <ИМЯ ВЫВОДА> -pinname <НОМЕР ВЫВОДА В КОРПУСЕ ИМС> set_io clock -pinname A4 set_io reset -pinname A1 set_io code\[0\] -pinname A2 set_io code\[1\] -pinname A3 set_io code\[2\] -pinname A5 set_io code\[3\] -pinname A6

Отметим, что при назначении выводов для векторных сигналов перед каждой квадратной скобкой нужно поставить знак «\».

Синтез

Для проведения синтеза следует сделать двойной щелчок мышью на пункте Synthesize в окне Design Flow. После этого автоматически запустится синтезатор Synplify, вмешательство в его работу не потребуется. По окончании синтеза протоколы Synplify (так же, как Modelsim, компилятора и трассировщика) можно просмотреть, нажав в окне Design Flow кнопку Open Reports (с изображением двух листков бумаги с загнутыми уголками). Очень полезно избавиться от максимально возможного количества предупреждений (Warnings). Например, на этом этапе можно обнаружить несовпадение списков чувствительности процессов VHDL и реально используемых сигналов. Это, как известно, может привести к ошибкам во время функционального моделирования, которые могли быть не замечены ранее. В нашем простом проекте ни одного предупреждения не возникло.

Если сделать двойной щелчок мышью по пункту Simulation под строкой Synthesize, то сначала пройдет синтез (если нет ошибок), а потом запустится моделирование по результатам синтеза. Что-то менять в интерфейсе между Libero и Modelsim необязательно. В нашем случае результат не будет отличаться от результата функционального моделирования, за исключением появления небольших задержек срабатывания относительно фронтов тактовой частоты. Но здесь мы бы уже не смогли посмотреть сигнал counter4, так как он удален при синтезе.

Компиляция и трассировка

Мы можем упростить себе работу, сразу сделав в окне Design Flow двойной щелчок мышью на строке Simulate под пунктом Place and Route. После этого последовательно выполнятся компиляция, трассировка и моделирование результата трассировки. Если не будет найдено ошибок, то Modelsim покажет картину, очень близкую к реальности.

На этом работа над проектом закончена. Осталось подключить программатор и прошить ПЛИС.

Заключение

Мы прошли самое начало пути в освоении САПР Libero SoC для работы с ПЛИС фирмы Microsemi. За рамками статьи осталось много интересных и нужных тем. Но если разработчик, впервые приступающий к работе с Libero SoC, теперь знает, с чего начать, то цель статьи достигнута.

Упомянутые в статье файлы проекта можно найти в Интернете [6].

- www.microsemi.com

- Менеджер загрузок Download Master — http://www.westbyte.com/dm/

- Тема «Редакторы HDL, альтернатива» на форуме разработчиков электроники ELECTRONIX.ru в разделе «Программируемая логика ПЛИС (FPGA,CPLD, PLD) > Среды разработки — обсуждаем САПРы» —http://electronix.ru/forum/index.php?showtopic=29129

- Тестовый редактор Notepad++ — http://notepad-plus-plus.org/

- Libero IDE Quick Start Guide — http://www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=131533

- http://dsioffe.narod.ru/articles/libero/counter.zip

4 августа, 2020

4 августа, 2020 23 ноября, 2023

23 ноября, 2023