Изучение основ цифровой обработки сигналов с помощью учебного лабораторного стенда LESO2.1

Рассмотрим проектирование цифрового автомата более простым способом — методом умножения в столбик. Управляющий автомат умножителя разработаем посредством редактора состояний САПР Quartus II (State Machine Viewer). Далее реализуем умножитель размерностью 4×4 в базисе ПЛИС типа ППВМ серии Cyclone EP1C3T144C8N фирмы Altera с помощью учебного лабораторного стенда LESO2.1 (Лаборатории электронных средств обучения, ЛЭСО ГОУ ВПО «СибГУТИ») отечественной разработки [5]. Учебный лабораторный стенд предназначен для обучения основам проектирования цифровой техники на основе ПЛИС.

Поскольку Quartus II Web Edition version 13.0.1 сборка 232 не поддерживает ПЛИС серии Cyclone, необходимо перейти на более раннюю версию Quartus II Web Edition version 9.1.

За основу схемы умножителя P=B (множимое)×A (множитель) возьмем пример из [6]. На рис. 1 и 2 показаны верхний и нижний уровни иерархии проекта умножителя размерностью 4×4. Сигнал А (множитель) следует рассматривать как число, а сигнал B как константу (множимое). Умножитель настроен на умножение двух чисел 10×10. Умножитель состоит из двух однотипных регистров ShiftN, сдвигающих влево или вправо в зависимости от сигнала DIR, задающего направление сдвига (пример 1), детектора нуля AllZero, управляющего автомата avt на пять состояний (пример 2), 8‑разрядного сумматора на мегафункции lpm_add_sub, шинного мультиплексора на мегафункции lpm_mux и 8‑разрядного регистра на мегафункции lpm_dff, выполняющего роль аккумулятора. Один из регистров ShiftN (DIR=0), на вход которого подается число A, работает как преобразователь параллельного кода в последовательный, параллельный выход SRA[7…0] нужен лишь для детектирования нуля.

Пример 1. Сдвиговый регистр на языке VHDL

LIBRARY ieee; USE ieee.std_logic_1164.all; entity ShiftN is port(CLK, CLR, LD, SH, DIR: in STD_LOGIC; D: in std_logic_vector(3 downto 0); Q: out std_logic_vector(7 downto 0)); end ShiftN; architecture a of ShiftN is begin process (CLR, CLK) variable St: std_logic_vector(7 downto 0); subtype InB is natural range 3 downto 0; begin if CLR = '1' then St := (others => '0'); Q <= St; elsif CLK'EVENT and CLK='1' then if LD = '1' then St:=(others=>'0'); St(InB) := D; Q <= St; elsif SH = '1' then case DIR is when '0' => St := '0' & St(St'LEFT downto 1); St := St(St'LEFT-1 downto 0) & '0'; end case; Q <= St; end if; end if; end process; end a;

Пример 2. Код языка VHDL управляющего автомата

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY avt IS PORT ( res : IN STD_LOGIC; clk : IN STD_LOGIC; Start : IN STD_LOGIC; LSB : IN STD_LOGIC; Stop : IN STD_LOGIC; Done : OUT STD_LOGIC; Init : OUT STD_LOGIC; Add : OUT STD_LOGIC; Shift : OUT STD_LOGIC ); END avt; ARCHITECTURE BEHAVIOR OF avt IS TYPE type_fstate IS (Check_FS,Init_FS,Adder_FS,shift_FS,End_mult); SIGNAL fstate : type_fstate; SIGNAL reg_fstate : type_fstate; BEGIN Init <='1' when reg_fstate = Init_FS else '0'; Add <='1' when reg_fstate = Adder_FS else '0'; Shift <='1' when reg_fstate = shift_FS else '0'; Done <='1' when reg_fstate = End_mult else '0'; process (clk, res) begin if res = '1' then reg_fstate <= End_mult; elsif clk'event and clk = '1' then case reg_fstate is when Init_FS => reg_fstate <= Check_FS; when Check_FS => if LSB = '1' then reg_fstate <= Adder_FS; elsif Stop ='0' then reg_fstate <= shift_FS; else reg_fstate <= End_mult; end if; when Adder_FS => reg_fstate <= shift_FS; when shift_FS => reg_fstate <= Check_FS; when End_mult => if Start = '1' then reg_fstate <= Init_FS; end if; end case; end if; end process; END BEHAVIOR;

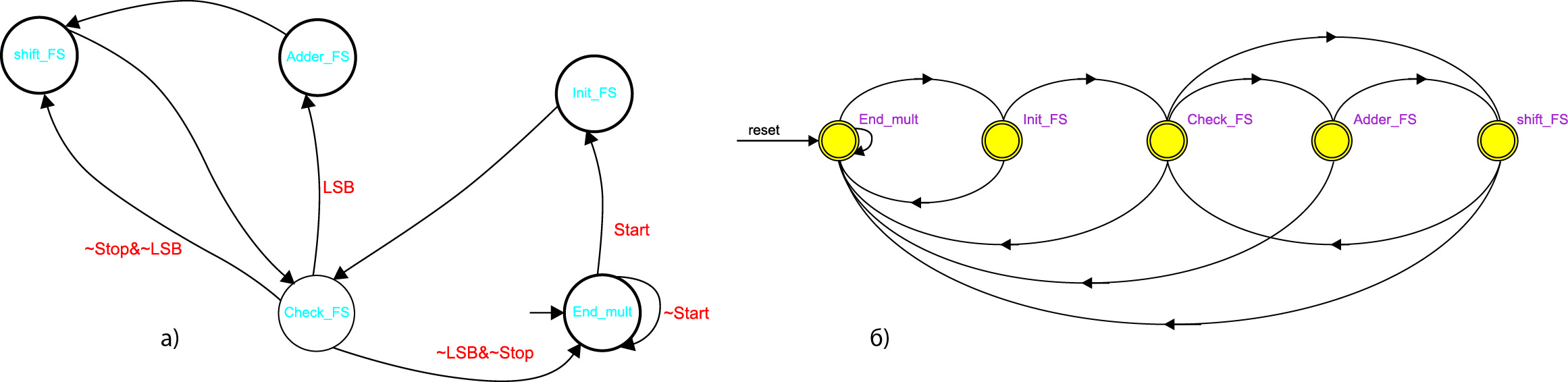

На рис. 3 продемонстрирован принцип работы управляющего автомата. Автомат принимает пять состояний с именами Check_FS, Init_FS, Adder_FS, shift_FS, End_mult. В каждом из состояний активен один из сигналов Init, Add, Shift и Done. Автомат разработан по классической схеме, с использованием одного оператора Process (однопроцессный шаблон) для описания памяти состояний и логики переходов.

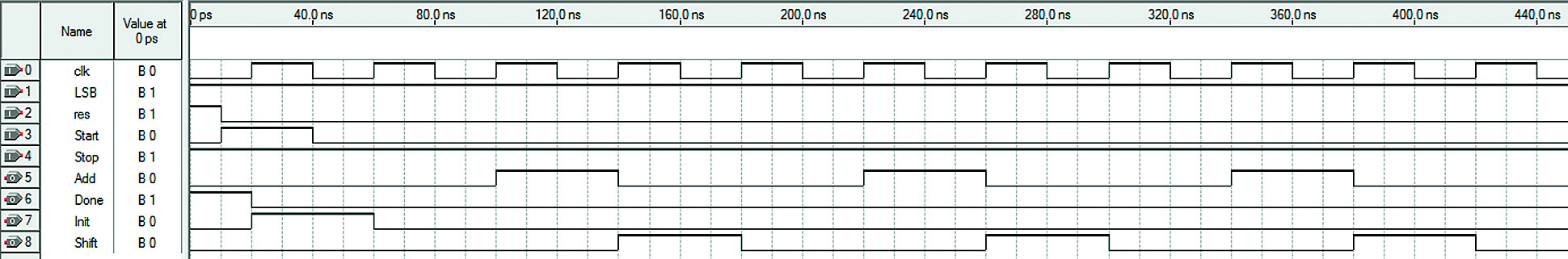

Автомат инициализируется высоким уровнем сигнала Start, синхронизируемого синхросигналом clk, переводящим выход Init в активное состояние. При высоком уровне сигнала Init происходит загрузка обоих сдвиговых регистров параллельным кодом. Если на вход LSB все время будет поступать логическая 1 (младший разряд SRA[0] 8‑разрядного сигнала SRA[7..0]) с выхода сдвигового регистра ShiftN при DIR=0, то управляющий автомат будет вырабатывать не перекрывающиеся сигналы «сдвинуть» (Shift) и «сложить» (Add). Это возможно, например, при загрузке числа 15D (1111BIN). На рис. 4 показан пример умножения чисел 10×10. Результат 100. По окончании процесса умножения вырабатывается сигнал готовности Done.

Разработаем цифровой автомат с применением встроенного редактора состояний конечного автомата (рис. 5) и извлечем код языка VHDL в автоматическом режиме. Используется двухпроцессный шаблон. Первый оператор Process описывает блок регистров (память состояний) для хранения состояний автомата. Второй оператор Process предназначен для описания логики переходов и логики формирования выхода (пример 3). Тестирование умножителя на примере умножения 5×5 показано на рис. 6. Общие сведения по числу задействованных ресурсов в проекте представлены в таблице.

Рис. 5. Граф-автомат:

а) разработанный с помощью редактора состояний;

б) синтезированный граф-автомат (меню Netlist Viewers/State Machine Viewer)

|

Общее число логических элементов (Logic Cells, LC) |

47 |

|

Количество триггеров логических элементов (LC Registers) |

41 |

|

Количество таблиц перекодировок (LUT-only LC) |

6 |

|

Рабочая частота в наихудшем случае Fmax, МГц |

275 |

Пример. 3. VHDL-код, извлеченный в автоматическом режиме из граф-автомата, созданного с помощью редактора состояний в САПР Quartus II

- Generated by Quartus II Version 9.0 Build 132 02/25/2009 SJ Full Version -- Created on Wed Mar 05 14:25:18 2014 LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY avt_flow IS PORT ( reset : IN STD_LOGIC := '0'; clock : IN STD_LOGIC; Start : IN STD_LOGIC := '0'; LSB : IN STD_LOGIC := '0'; Stop : IN STD_LOGIC := '0'; Done : OUT STD_LOGIC; Init : OUT STD_LOGIC; Add : OUT STD_LOGIC; Shift : OUT STD_LOGIC ); END avt_flow; ARCHITECTURE BEHAVIOR OF avt_flow IS TYPE type_fstate IS (Check_FS,Init_FS,Adder_FS,shift_FS,End_mult); SIGNAL fstate : type_fstate; SIGNAL reg_fstate : type_fstate; BEGIN PROCESS (clock,reg_fstate) BEGIN IF (clock='1' AND clock'event) THEN fstate <= reg_fstate; END IF; END PROCESS; PROCESS (fstate,reset,Start,LSB,Stop) BEGIN IF (reset='1') THEN reg_fstate <= End_mult; Done <= '0'; Init <= '0'; Add <= '0'; Shift <= '0'; ELSE Done <= '0'; Init <= '0'; Add <= '0'; Shift <= '0'; CASE fstate IS WHEN Check_FS => IF ((NOT((LSB = '1')) AND (Stop = '1'))) THEN reg_fstate <= End_mult; ELSIF ((LSB = '1')) THEN reg_fstate <= Adder_FS; ELSIF ((NOT((Stop = '1')) AND NOT((LSB = '1')))) THEN reg_fstate <= shift_FS; -- Inserting 'else' block to prevent latch inference ELSE reg_fstate <= Check_FS; END IF; WHEN Init_FS => reg_fstate <= Check_FS; Init <= '1'; WHEN Adder_FS => reg_fstate <= shift_FS; Add <= '1'; WHEN shift_FS => reg_fstate <= Check_FS; Shift <= '1'; WHEN End_mult => IF ((Start = '1')) THEN reg_fstate <= Init_FS; ELSIF (NOT((Start = '1'))) THEN reg_fstate <= End_mult; -- Inserting 'else' block to prevent latch inference ELSE reg_fstate <= End_mult; END IF; Done <= '1'; WHEN OTHERS => Done <= 'X'; Init <= 'X'; Add <= 'X'; Shift <= 'X'; report "Reach undefined state"; END CASE; END IF; END PROCESS; END BEHAVIOR;

Стенд подключается к персональному компьютеру через USB-порт. Для записи файла конфигурации в память ПЛИС через USB-порт персонального компьютера требуется преобразовать *.sof-файл в формат с расширением *.rbf. Загрузка конфигурационного файла в ПЛИС производится с помощью отдельной программы-загрузчика (l2flash.exe) [5].

Входные и выходные контакты к внешним выводам ПЛИС подключены с помощью меню Assignments/Pins (рис. 7). Из-за того что стенд имеет 8 переключателей S1–S8, пришлось отказаться от загрузки чисел с внешних портов (4‑разрядные сигналы A и B) и от сигнала Done, поскольку доступно всего лишь 8 светодиодов. Умножаемые числа предварительно сохраняются в константах (мегафункция LPM_constant). Далее необходимо следовать рис. 6 и 7. Светодиоды LED1‑LED8 отображают результат умножения (8‑разрядный сигнал Product[7..0]). В проекте принято, что LED8 (pin 121) — это младший значащий разряд.

Для подачи тактовых импульсов с помощью кнопки Bottom рекомендуется использовать блок Antitinkling. Данный блок предназначен для подавления дребезга контактов [5]. Из-за этого явления непосредственное подключение кнопки с механическим замыканием контактов к цифровой схеме не всегда допустимо. Суть дребезга заключается в многократном неконтролируемом замыкании и размыкании контактов в момент коммутации, в результате чего на цифровую схему подается множество импульсов вместо одного.

Частота тактового генератора в учебных стендах LESO2 равна 6 МГц, в стендах LESO2.1 и LESO2.3 — 50 МГц. Делитель частоты должен обеспечить интервал между импульсами больше, чем длительность дребезга, и меньше, чем длительность нажатия кнопки. На рис. 8 показана схема подавителя дребезга с использованием суммирующего счетчика-делителя частоты. Такое простое решение выбрано в силу учебного характера выполняемого проекта. В настоящее время для ПЛИС, реализуемых по технологическим процессам с нормами 90 нм и ниже, рекомендуется использовать фильтры подавления дребезга контактов совместно со схемами фазовой автоподстройки частоты (ФАПЧ) [7]. В ПЛИС серии Artix‑7 фирмы Xilinx это блоки управления синхронизацией Clock Management Tile (CMT), включающие комбинированные модули управления синхронизацией Mixed-Mode Clock Managers (MMCM). Например, в [7] показан проект на ПЛИС XC7A100N со схемой подавления дребезга контактов. Сигнал с кварцевого генератора с частотой 100 МГц подключен к синтезатору тактовой частоты (через специальный входной буфер типа IBUFG), который обеспечивает формирование дочернего тактового сигнала с частотой 166 МГц. Далее сигнал с частотой 166 МГц поступает на делитель частоты с коэффициентом 131072, на выходе которого формируется сигнал с частотой 1,27 кГц, являющийся сигналом разрешения тактирования фильтров (работают на частоте 166 МГц, как и весь проект в целом). Данный сигнал (CEO_1K27) устанавливается в единицу в течение одного такта частоты 166 МГц, после чего 131 071 такт находится в нуле. Таким образом, единичные однотактовые импульсы высокого уровня разрешают переключение внутренних счетчиков фильтров с частотой 1,27 кГц [7].

Рис. 8.

а) Подавитель дребезга с использованием суммирующего счетчика-делителя частоты;

б) временные диаграммы его работы

В нашем случае 19‑разрядный счетчик обеспечивает коэффициент счета 524 287 и выходной сигнал cout с пониженной частотой 95,37 Гц (100 Гц — период 10 мс). Время дребезга кнопки составляет примерно 2 мс.

На рис. 9 показано тестирование умножителя на примере умножения 5×5. Тестирование осуществляется следующим образом. Согласно рис. 6 щелкаем переключателем S2 (pin 50), выполняющим роль асинхронного сигнала res. Переводим в верхнее положение переключатель S3 (pin 51) — сигнал start, далее нажимаем на кнопку Button (pin 37) один раз, происходит загрузка чисел в умножитель. Переводим переключатель S3 в нижнее положение. Щелкаем три (рис. 9а) и пять раз (рис. 9б) кнопкой Button для имитации подачи синхросигнала. Итоговый результат умножения — десятичное число 25, а процесс умножения осуществляется за 9 тактов синхрочастоты.

Рис. 9. Тестирование умножителя на примере умножения 5×5:

а) промежуточный результат 5;

б) итоговый результат 25

Запрограммировать ПЛИС возможно с помощью Altera USB Blaster без предварительного преобразования *.sof-файла в формат *.rbf (рис. 10). Программирование осуществляется непосредственно в САПР Quartus II (меню Tools/Programmer). В этом случае питание лабораторного стенда LESO2.1 реализуется через USB-кабель, а программирование выполняется через JTAG-интерфейс.

Выводы

Учебный лабораторный стенд LESO2.1 отечественной разработки содержит хороший функциональный набор для занятий по цифровой схемотехнике и может быть использован для изучения основ проектирования комбинационных и последовательностных устройств.

Статья опубликована в журнале «Компоненты и технологии» №5’2014

- Строгонов А., Быстрицкий А. Проектирование умножителя методом правого сдвига и сложения с управляющим автоматом в базисе ПЛИС // Компоненты и технологии. 2013. № 12.

- Строгонов А., Винокуров А., Джиоти А. Проектирование умножителя целых чисел со знаком методом правого сдвига и сложения в базисе ПЛИС // Компоненты и технологии. 2014. № 1.

- Computer Arithmetic: Algorithms and Hardware Designs (Oxford U. Press, 2nd ed., 2010, ISBN 978-0-19-532848-6).

- Строгонов А., Быстрицкий А., Джиоти А. Проектирование КИХ-фильтра на умножителе методом правого сдвига и сложения в базисе ПЛИС // Компоненты и технологии. 2014. № 1.

- Учебный лабораторный стенд LESO2.1. Паспорт и Инструкция по эксплуатации. Новосибирск. 2009. labfor.ru

- http://www.csit-sun.pub.ro/resources/asic/CH10.pdf

- Борисенко Н. Модель узла управления динамическим 7‑сегментным индикатором с подавлением дребезга контактов кнопок в объеме ПЛИС Xilinx Artix‑7 для отладочной платы Digilent Nexys 4 // Компоненты и технологии. 2014. № 2.

4 августа, 2020

4 августа, 2020 27 июня, 2022

27 июня, 2022 19 июня, 2020

19 июня, 2020