Проектирование конечных автоматов с использованием пакетов расширения Stateflow и Xilinx System Generator системы Matlab/Simulink

Первичные сведения по конечным автоматам

Теоретические сведения по конечным автоматам можно получить в учебном пособии [1], раздел 7.3.4 «Анализ конечных автоматов с D‑триггерами», и в работе [2]. Обычно рассматривают два типа автоматов: автомат Мили (Mealy) и Мура (Moore). Выход автомата Мура является функцией только текущего состояния, выход автомата Мили — функция как текущего состояния, так и начального внешнего воздействия. Конечный автомат состоит из трех основных частей (рис. 1) [1]:

- Регистр текущего состояния. Этот регистр представляет собой набор тактируемых D‑триггеров, синхронизируемых одним синхросигналом, и используется для хранения кода текущего состояния автомата. Для автомата с n состояниями требуется Log2(n) триггеров.

- Логика переходов. Конечный автомат может находиться в каждый конкретный момент времени только в одном состоянии. Каждый тактовый импульс вызывает переход автомата из одного состояния в другое. Правила перехода определяются комбинационной схемой, называемой логикой переходов. Следующее состояние определяется как функция текущего состояния и входного воздействия.

- Логика формирования выхода. Выход цифрового автомата обычно определяется как функция текущего состояния и исходной установки (в случае автомата Мили). Формирование выходного сигнала автомата определяется с помощью логики формирования выхода.

- Формальное определение конечного автомата можно дать в следующем виде [1]:

- Следующее состояние = F (текущее состояние, вход).

- Выход = G (текущее состояние, вход).

На рис. 2 показан тактируемый синхронный конечный автомат Мили с D‑триг-герами, переключающимися по положительному фронту. Данная схема выполняет функцию 2‑разрядного двоичного синхронного счетчика. Для сравнения посмотрите принципиальную схему синхронного двоичного счетчика на ИС типа SN74163. Логика переходов есть не что иное, как входные мультиплексоры на входах D‑триггеров ИС типа SN74163.

Рис. 2. Тактируемый синхронный конечный автомат Мили с D триггерами, переключающимися по положительному фронту синхросигнала

На рис. 3 представлена диаграмма состояний (переходов) конечного автомата на четыре состояния. Схема переходит из состояния в состояние по переднему фронту синхроимпульса при наличии сигнала логической единицы на входе EN. При переходе из состояния 3 в состояние 0 на выходе схемы формируется сигнал MAX (аналог сигнала выхода переноса Cout, используемого в счетчиках, позволяет построить счетчики с произвольным модулем счета). Он равен логической единице, когда равны единице биты, хранящиеся во всех разрядах счетчика, и подан сигнал разрешения EN.

Пример проектирования автомата Мили (Mealy) с использованием пакета расширения Stateflow системы Matlab/Simulink и САПР ПЛИС Xilinx ISE Design Suite

Система Matlab/Simulink содержит встроенный генератор кода языка описания аппаратных средств HDL (Simulink HDL Coder. Simulink HDL Coder — программный продукт для генерации VHDL-кода без привязки к конкретной архитектуре ПЛИС и платформе по Simulink-моделям и граф-автоматам, Stateflow-диаграммы).

Дополнительную информацию по применению системы Matlab/Simulink с пакетом расширения Stateflow и САПР Quartus II для разработки простейшего торгового автомата можно посмотреть в работе [3].

Разработаем имитационную модель 2‑разрядного синхронного суммирующего счетчика. В дальнейшем такую схему будем называть «конечный автомат». Входной сигнал EN на диаграмме переходов обозначается следующим образом: [EN==1]. Выходной сигнал MAX кодируется следующим образом:

{MAX=0} — счетчик находится в процессе счета;

{MAX=1} — счетчик досчитал до трех, «готов»

Квадратные скобки [] обозначают условие, фигурные {} — действие по условию. Запись [EN==1]{MAX=0} говорит о том, что выход автомата Мили является функцией как текущего состояния, так и начального внешнего воздействия, то есть от сигнала EN.

Автомат может принимать четыре состояния (рис. 4): st0, st1, st2 и st3 в соответствии с рис. 3. На вход автомата EN задается тестовая последовательность из набора единиц. Для того чтобы извлечь VHDL-код из диаграммы переходов, необходимо в свойствах диаграммы Properties (правый клик мышки) в поле Execute (enter) Chart At Initialization поставить галочку (рис. 4г).

Рис. 4. Модель конечного автомата Мили в системе Matlab/Simulink с использованием Stateflow-диаграммы:

а) верхний уровень;

б) нижний уровень иерархии;

в) диаграмма переходов, разработанная с помощью пакета расширения Stateflow;

г) свойства диаграммы

После того как будет создана модель конечного автомата, необходимо выбрать численный метод решения системы дифференциальных уравнений. C помощью проводника модели (Model Explorer) выбираем дискретный метод решения (discrete) дифференциальных уравнений в настройках Solver и настраиваем генератор кода языка VHDL в меню HDL coder. Результат имитационного моделирования показан на рис. 4. На рис. 5 представлено имитационное моделирование конечного автомата.

Пример 1 демонстрирует код автомата Мили с регистерным выходом на языке VHDL, полученный с использованием Simulink HDL Coder системы Matlab/Simulink. Анализируя полученный VHDL-код в автоматическом режиме, можно сделать вывод, что используется двухпроцессный шаблон описания конечного автомата и перечисляемый тип данных (Enumerated type) T_state_type_is_Chart, который описан в пакете USE work.Avt_pkg (пример 2). Перечисляемый тип — такой тип данных, при котором количество всех возможных состояний конечно. Этот тип наиболее часто используется для обозначений состояний конечных автоматов. Любой перечисляемый тип имеет внутреннюю нумерацию: первый элемент всегда имеет номер 0, второй — 1 и т. д. Первый оператор PROCESS со списком чувствительности (clk, reset) описывает память состояний конечного автомата, а второй оператор PROCESS со списком чувствительности (is_Chart, En, MAX_reg) описывает логику переходов и логику формирования выхода.

Пример 1. Код автомата Мили с регистерным выходом на языке VHDL, полученный с использованием Simulink HDL Coder системы Matlab/Simulink

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; USE work.Avt_pkg.ALL; ENTITY Avt IS PORT( clk : IN std_logic; reset : IN std_logic; clk_enable : IN std_logic; En : IN real; -- double ce_out : OUT std_logic; MAX : OUT real -- double ); END Avt; ARCHITECTURE rtl OF Avt IS -- Signals SIGNAL enb : std_logic; SIGNAL is_Chart : T_state_type_is_Chart; -- uint8 SIGNAL MAX_1 : real := 0.0; -- double SIGNAL MAX_reg : real := 0.0; -- double SIGNAL is_Chart_next : T_state_type_is_Chart; -- enumerated type (4 enums) SIGNAL MAX_reg_next : real := 0.0; -- double BEGIN enb <= clk_enable; Chart_process : PROCESS (clk, reset) BEGIN IF reset = '1' THEN MAX_reg <= 0.0; is_Chart <= IN_st0; ELSIF clk'EVENT AND clk = '1' THEN IF enb = '1' THEN is_Chart <= is_Chart_next; MAX_reg <= MAX_reg_next; END IF; END IF; END PROCESS Chart_process; Chart_output : PROCESS (is_Chart, En, MAX_reg) BEGIN is_Chart_next <= is_Chart; MAX_reg_next <= MAX_reg; CASE is_Chart IS WHEN IN_st0 => IF En = 1.0 THEN MAX_reg_next <= 0.0; is_Chart_next <= IN_st1; END IF; WHEN IN_st1 => IF En = 1.0 THEN MAX_reg_next <= 0.0; is_Chart_next <= IN_st2; END IF; WHEN IN_st2 => IF En = 1.0 THEN MAX_reg_next <= 0.0; is_Chart_next <= IN_st3; END IF; WHEN OTHERS => IF En = 1.0 THEN MAX_reg_next <= 1.0; is_Chart_next <= IN_st0; END IF; END CASE; END PROCESS Chart_output; MAX_1 <= MAX_reg_next; ce_out <= clk_enable; MAX <= MAX_1; END rtl;

Пример 2. Пакет, в котором описан перечисляемый тип данных T_state_type_is_Chart

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; PACKAGE Avt_pkg IS TYPE T_state_type_is_Chart IS (IN_st0, IN_st1, IN_st2, IN_st3); END Avt_pkg;

Для того чтобы на базе этого кода создать проект в САПР ISE, нужно тип real, относящийся к внешним сигналам En, MAX и внутренним MAX_1, MAX_reg, MAX_reg_next, заменить на тип std_logic, при этом также обеспечить замену 0.0 на «0» и 1.0 на «1» (пример 3). Далее следует разработать испытательный стенд (пример 4). На рис. 6 показано функциональное моделирование конечного автомата.

Пример 3. Отредактированный код автомата Мили на языке VHDL, полученный с использованием Simulink HDL Coder системы Matlab/Simulink

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; USE work.Avt_pkg.ALL; ENTITY Avt IS PORT( clk : IN std_logic; reset : IN std_logic; clk_enable : IN std_logic; En : IN std_logic; ce_out : OUT std_logic; MAX : OUT std_logic); END Avt; ARCHITECTURE rtl OF Avt IS -- Signals SIGNAL enb : std_logic; SIGNAL is_Chart : T_state_type_is_Chart; SIGNAL MAX_1 : std_logic; SIGNAL MAX_reg : std_logic; SIGNAL is_Chart_next : T_state_type_is_Chart; SIGNAL MAX_reg_next : std_logic; BEGIN enb <= clk_enable; Chart_process : PROCESS (clk, reset) BEGIN IF reset = '1' THEN MAX_reg <= '0'; is_Chart <= IN_st0; ELSIF clk'EVENT AND clk = '1' THEN IF enb = '1' THEN is_Chart <= is_Chart_next; MAX_reg <= MAX_reg_next; END IF; END IF; END PROCESS Chart_process; Chart_output : PROCESS (is_Chart, En, MAX_reg) BEGIN is_Chart_next <= is_Chart; MAX_reg_next <= MAX_reg; CASE is_Chart IS WHEN IN_st0 => IF En = '1' THEN MAX_reg_next <= '0'; is_Chart_next <= IN_st1; END IF; WHEN IN_st1 => IF En = '1' THEN MAX_reg_next <= '0'; is_Chart_next <= IN_st2; END IF; WHEN IN_st2 => IF En = '1' THEN MAX_reg_next <= '0'; is_Chart_next <= IN_st3; END IF; WHEN OTHERS => IF En = '1' THEN MAX_reg_next <= '1'; is_Chart_next <= IN_st0; END IF; END CASE; END PROCESS Chart_output; MAX_1 <= MAX_reg_next; ce_out <= clk_enable; MAX <= MAX_1; END rtl;

Пример 4. Испытательный стенд автомата Мили

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

LIBRARY UNISIM;

USE UNISIM.Vcomponents.ALL;

ENTITY avt_sch_avt_sch_sch_tb IS

END avt_sch_avt_sch_sch_tb;

ARCHITECTURE behavioral OF avt_sch_avt_sch_sch_tb IS

COMPONENT avt_sch

PORT( clk : IN STD_LOGIC;

ares : IN STD_LOGIC;

clk_ena : IN STD_LOGIC;

en : IN STD_LOGIC;

ce_out : OUT STD_LOGIC;

MAX : OUT STD_LOGIC);

END COMPONENT;

SIGNAL clk : STD_LOGIC;

SIGNAL ares : STD_LOGIC:= '0';

SIGNAL clk_ena : STD_LOGIC:= '1';

SIGNAL en : STD_LOGIC:= '1';

SIGNAL ce_out : STD_LOGIC;

SIGNAL MAX : STD_LOGIC;

-- Clock period definitions

constant clk_period : time := 100 ns;

BEGIN

UUT: avt_sch PORT MAP(

clk => clk,

ares => ares,

clk_ena => clk_ena,

en => en,

ce_out => ce_out,

MAX => MAX

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

tb : process

begin

wait for 100 ns;

en <= '1';

wait for 100 ns;

en <= '1';

wait for 100 ns;

en <= '1';

wait for 100 ns;

en <= '1';

wait;

end process;

END;

Пример проектирования автомата Мура с использованием методологии Black Boxes Xilinx System Generator

Рассмотрим трехпроцессный шаблон описания работы конечного автомата Мура (рис. 7, пример 5). В данном случае применяются два сигнала state и next_state перечисляемого типа и три оператора Process. Проект разработаем в САПР ПЛИС Altera Quartus II v13.1 Build 162 c использованием ModelSim Altera Started Edition 10.1 d. Для кодирования состояний цифрового автомата будем использовать метод one hot encoding (ОНЕ — кодирование с одним активным, или горячим состоянием, или унитарное кодирование). Кодирование по методу OHE будет определено явно в коде языка VHDL с использованием атрибута syn_encoding “onehot” [2, 5].

Пример. 5. Трехпроцессный шаблон описания конечного автомата на языке VHDL с использованием атрибута syn_encoding «onehot»

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY counter2 IS

PORT(

en,res,clk,ce : IN STD_LOGIC;

Max : OUT STD_LOGIC

);

END counter2;

ARCHITECTURE a OF counter2 IS

TYPE state_values IS (Stage0, Stage1, Stage2, Stage3);

signal state, next_state: state_values;

attribute syn_encoding: string;

attribute syn_encoding of state, next_state: signal is "onehot";

BEGIN

statereg: process(clk,ce,res)

begin

if res = '1' then state<=Stage0;

elsif (clk'event and clk='1') then

if ce = '1' then state<=next_state;

end if;

end if;

end process statereg;

process(state, en)

begin

case state is

when Stage0=>

IF en='1' THEN next_state<=Stage1;

else next_state<=Stage0;

END IF;

when Stage1=>

IF en='1' THEN next_state<=Stage2;

else next_state<=Stage1;

END IF;

when Stage2=>

IF en='1' THEN next_state<=Stage3;

else next_state<=Stage2;

END IF;

when Stage3=>

IF en='1' THEN next_state<=Stage0;

else next_state<=Stage3;

END IF;

when others=>

next_state<=Stage0;

end case;

end process;

process (state)

begin

case state is

when Stage0=>

MAX <= '0';

when Stage1=>

MAX <= '0';

when Stage2=>

MAX <= '0';

when Stage3=>

MAX <= '1';

end case;

end process;

END a;

Метод получил такое название потому, что в каждый конкретный момент времени активным (hot) может быть только один триггер состояния. Применение метода ОНЕ для ПЛИС по архитектуре ППВМ наиболее перспективно [4, 5]. Метод ОНЕ применительно к ПЛИС по архитектуре ППВМ дает возможность строить конечные автоматы, которые в общем случае требуют меньших ресурсов и отличаются более высокими скоростными показателями, чем аналогичные конечные автоматы с двоичным кодированием состояний. Повышенное быстродействие по методу ОНЕ обеспечивается меньшим числом уровней логики между рабочими фронтами синхросигналов, чем в случае двоичного кодирования. Логические схемы при этом упрощаются, поскольку метод ОНЕ практически не требует логики декодирования состояний. Получающийся в результате построения конечного автомата набор триггеров похож на структуру типа сдвигового регистра.

Быстродействие конечного автомата типа ОНЕ остается постоянным с увеличением числа состояний. И напротив, быстродействие конечного автомата с высокой степенью кодирования состояний снижается с увеличением количества состояний, поскольку в этом случае для декодирования требуется большее число уровней логики с большим числом линий.

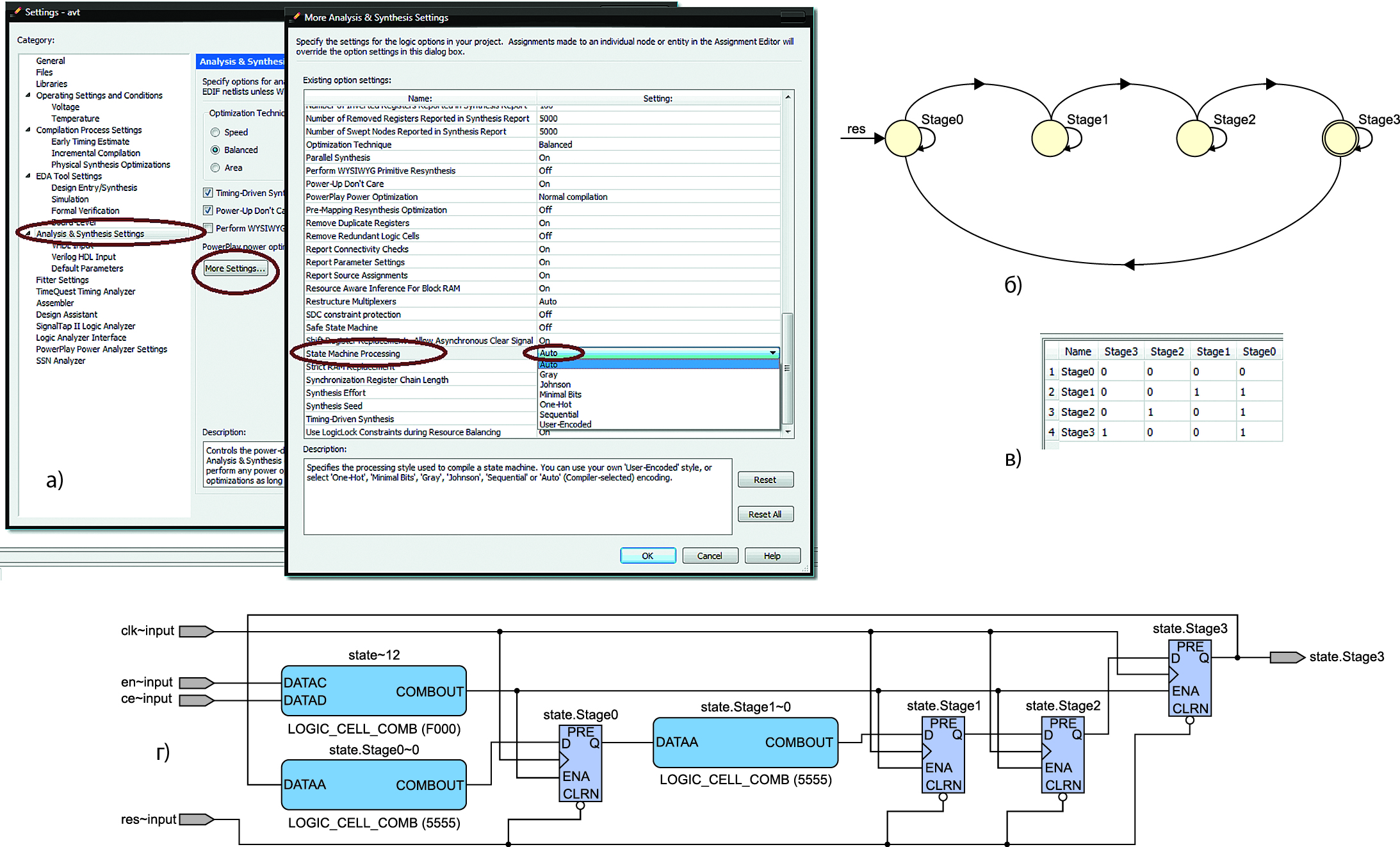

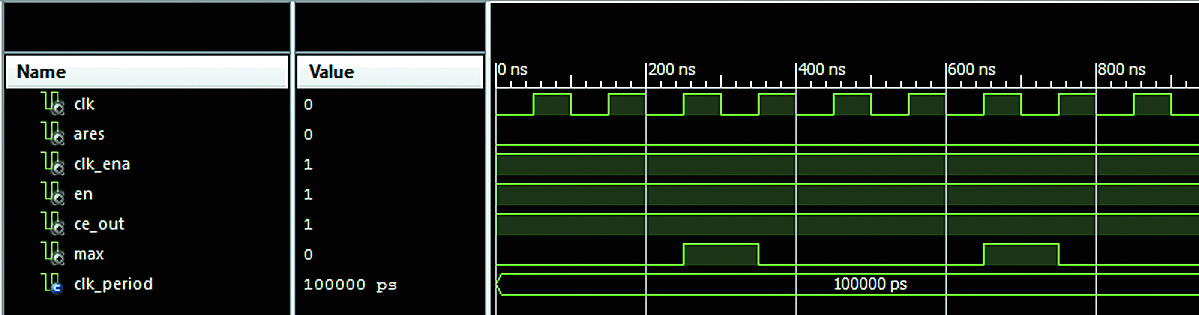

По умолчанию в настройках САПР Quartus II категория Analysis & Synthesis Settings/More Settings в разделе State Machine Processing задан режим Auto (рис. 8а). Отменим автоматическое кодирование перечисления и определим свои собственные коды с помощью атрибута enum_encoding (пример 5). Атрибут enum_encoding является строкой (string), содержащей набор векторов, по одному для каждого перечисляемого литерала в соответствующем типе. Первый вектор в строке атрибута определяет код для первого перечисляемого литерала, второй вектор — для второго литерала и т. д. Атрибут enum_encoding должен следовать сразу же за объявлением типа. Рис. 8б показывает восстановленную из кода языка VHDL диаграмму переходов, а рис. 8в демонстрирует таблицу переходов, соответствующую методу OHE. Полученный в результате синтеза конечный автомат с кодированием по методу OHE имеет структуру, похожую на сдвиговый регистр (рис. 8г). На рис. 9 показано функциональное моделирование конечного автомата в симуляторе ModelSim Altera Started Edition и в векторном редакторе САПР Quartus II. Демонстрируются изменения на сигналах state и next_state в процессе перехода по состояниям.

Рис. 8. Синтез конечного автомата по VHDL-коду в САПР Altera Quartus II (трехпроцессный шаблон):

а) настройки компилятора САПР Quartus II для синтеза конечного автомата (по умолчанию выбран стиль кодирования auto);

б) граф-автомат, восстановленный из VHDL-кода;

в) таблица переходов, демонстрирующая использование метода OHE;

г) структура сдвигового регистра в основе автомата с кодированием по методу OHE на этапе размещения в технологический базис ПЛИС

Рис. 9. Функциональное моделирование конечного автомата в ModelSim Altera Started Edition и в векторном редакторе САПР Altera Quartus II

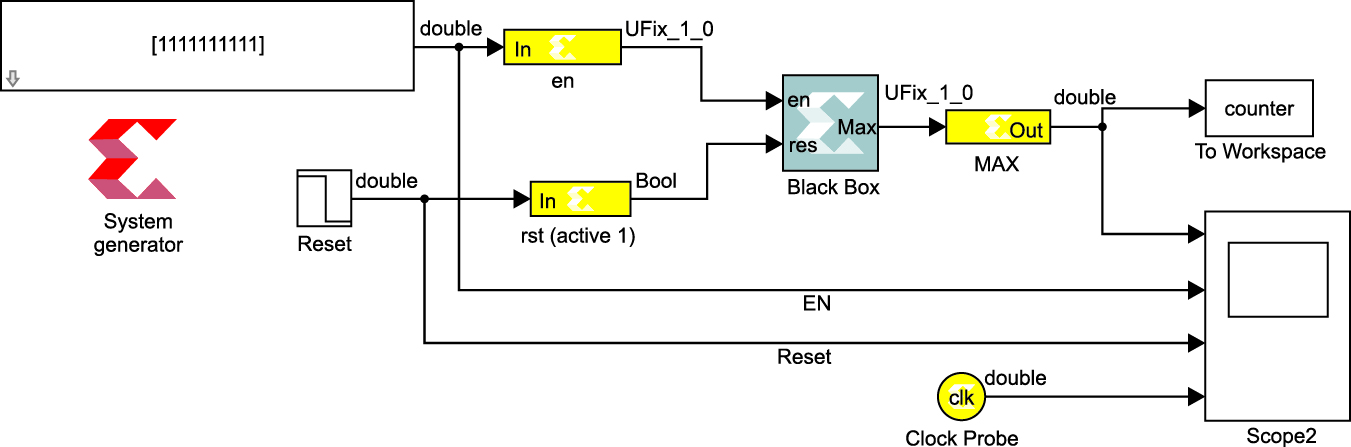

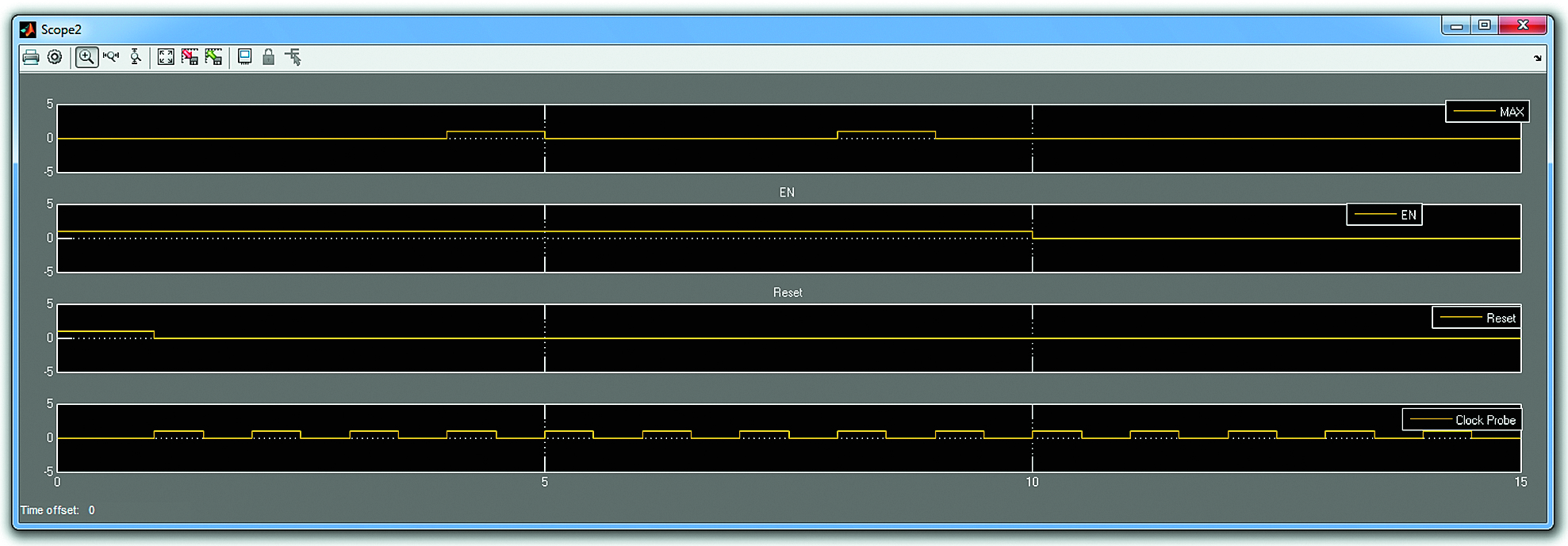

Убедившись с помощью временных диаграмм (рис. 9) в правильности функционирования конечного автомата, разработаем имитационную модель (рис. 10) в Matlab/Simulink с использованием единственного VHDL-файла и методологии Black Boxes Xilinx System Generator. Имитационное моделирование конечного автомата в системе Matlab/Simulink с применением VHDL-кода (функциональный блок Black Box) показано на рис. 11.

Рис. 10. Имитационная модель конечного автомата на основе функционального блока Black Box с использованием единственного VHDL-файла в системе Matlab/Simulink

Рис. 11. Имитационное моделирование конечного автомата в системе Matlab/Simulink с использованием единственного VHDL-файла (функциональный блок Black Box)

Посредством маркера Xilinx System Generator извлечем в автоматическом режиме оптимизированный VHDL-код и осуществим функциональное моделирование (рис. 12). С помощью рис. 11 и рис. 12 убеждаемся в правильности работы конечного автомата.

Предварительно удостоверимся, что в настройках компилятора ПЛИС Xilinx ISE Design Suite для синтеза конечного автомата по умолчанию выбран стиль кодирования auto (рис. 13). Рис. 14 показывает, что компилятор ПЛИС Xilinx ISE распознает атрибут syn_encoding “onehot” для сигналов state и next_state перечисляемого типа и применяет метод кодирования onehot. Однако таблица переходов отличается от той, что используется в САПР Altera Quartus II (рис. 8б). В САПР Quartus II используется инверсия младшего разряда таблицы переходов, то есть в состоянии, отличном от нулевого (начальное, st0), первый триггер в цепочке сдвигового регистра всегда активен. Тем не менее, сравнивая рис. 9 и 12, можно сделать вывод, что конечные автоматы, разработанные в САПР Altera и Xilinx, работают одинаково. Получаемая в результате синтеза структура сдвигового регистра в основе автомата с кодированием по методу OHE на этапе размещения в технологический базис ПЛИС Spartan‑6 xc6slx4-3tqg144 показана на рис. 15.

Рис. 13. Настройки компилятора ПЛИС Xilinx ISE Design Suite для синтеза конечного автомата (по умолчанию выбран стиль кодирования auto)

Рис. 15. Структура сдвигового регистра в основе автомата с кодированием по методу OHE на этапе размещения в технологический базис ПЛИС Spartan6 xc6slx4-3tqg144

Проектирование конечных автоматов с использованием функциональных блоков из библиотеки Reference Blockset/Control Logic Xilinx System Generator

На рис. 16 показано расположение функционального блока Mealy State Machine в библиотеке Xilinx Reference Blockset/Control Logic. На основе этого блока разработаем имитационную модель (рис. 17а) и проведем моделирование (рис. 17б). Предварительно необходимо отредактировать матрицу переходов и матрицу формирования выходного сигнала (рис. 18а) согласно рис. 3. Зададим разрядность выходного сигнала (1‑разрядный выходной сигнал MAX) и время дискретизации (1 с). На рис. 18б показана структурная схема автомата Мили, а на рис. 19 представлено функциональное моделирование в САПР Xilinx ISE.

Рис. 16. Расположение функционального блока Mealy State Machine в библиотеке Xilinx Reference Blockset/Control Logic

Рис. 17.

а) Имитационная модель конечного автомата на основе функционального блока Mealy State Machine, представленного на рис. 3;

б) результаты моделирования

Рис. 19. Функциональное моделирование конечного автомата на основе функционального блока Mealy State Machine в САПР Xilinx ISE

System Generator в автоматическом режиме создает файл проектных ограничений (avt_cw.ucf) по распространению сигналов, например исходя из требования к периоду синхросигнала (10 нс), указанного в настройках маркера System Generator (закладка Clocking, поле FPGA clock period). Параметр PERIOD задает ограничение на максимальное время распространения сигнала от выхода одного синхронного элемента до входа другого [6]. Максимальная рабочая частота проекта при заданных временных ограничениях для ПЛИС Spartan‑6 xc6slx4-3tqg144 на этапе post-map составляет 320 МГц. Для сравнения, кодирование автомата по методу OHE при тех же проектных ограничениях (NET “clk” TNM_NET = “clk_7796afde”; TIMESPEC “TS_clk_7796afde” = PERIOD “clk_7796afde” 10.0 ns HIGH 50%;) позволяет получить 578 МГц (рис. 20).

Выводы

Автоматически сгенерированный и оптимизированный VHDL-код по графу переходов, выполненный c использованием Simulink HDL Coder системы Matlab/Simulink, позволяет значительно упростить процесс разработки конечных автоматов для реализации их в различные технологические базисы ПЛИС. Использование объектно-ориентированного проектирования, предоставляемого Xilinx System Generator, в совокупности с методологией Black Boxes и с функциональными блоками из библиотеки Reference Blockset/Control Logic позволяет обеспечить не только имитационное моделирование в системе Matlab/Simulink, но и ускоренное проектирование конечных автоматов в САПР Xilinx ISE с гарантируемым быстродействием.

- Уэйкерли Дж. Ф. Проектирование цифровых устройств. Пер. с англ. М.: Постмаркет, 2002.

- Тарасов И. Методы и программные продукты для повышения производительности проектов на базе ПЛИС Xilinx // Компоненты и технологии. 2008. № 2.

- Строгонов А. Проектирование цифровых автоматов с использованием системы MATLAB/Simulink // Компоненты и технологии. 2008. № 4.

- Строгонов А. Проектирование конечных автоматов по методу OHE // Компоненты и технологии. 2007. № 10.

- Строгонов А., Быстрицкий А. Эффективность разработки конечных автоматов в базисе ПЛИС FPGA // Компоненты и технологии. 2013. № 1.

- Тарасов И. Методы и программные продукты для повышения производительности проектов на базе ПЛИС Xilinx // Компоненты и технологии. 2008. № 3.

4 августа, 2020

4 августа, 2020 23 ноября, 2023

23 ноября, 2023 27 июля, 2020

27 июля, 2020