Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии Vivado HLx Design Suite. Часть 21

Определение параметров управления процессами шифрования и дешифрования генерируемой конфигурационной последовательности

Для установки параметров управления процессами шифрования и дешифрования генерируемой конфигурационной последовательности проектируемого устройства необходимо открыть страницу Encryption диалоговой панели Edit Device Properties, как показано на рис. 1. Указанная страница включает два раздела: Encryption Settings и Key Settings, содержание которых зависит от семейства ПЛИС или программируемых систем на кристалле, выбранных для реализации разрабатываемого проекта. Это обусловлено тем, что различные серии кристаллов программируемой логики или расширяемых процессорных платформ поддерживают разные методы защиты конфигурационной информации. В ПЛИС серий Artix‑7, Kintex‑7 и Virtex‑7 и программируемых системах на кристалле семейства Zynq‑7000 AP SoC применяется шифрование и дешифрование конфигурационной последовательности в соответствии с алгоритмом AES (Advanced Encryption Standard), а также аутентификация с помощью алгоритма Hash Message Authentication Code (HMAC). Кристаллы программируемой логики и расширяемых процессорных платформ серий UltraScale и UltraScale+ используют для защиты конфигурационных данных новый алгоритм кодирования и декодирования AES-GCM (Advanced Encryption Standard — Galois/Counter Mode). Кроме того, эти кристаллы поддерживают возможность аутентификации конфигурационной последовательности согласно алгоритмам AES-GCM и RSA.

Рис. 1. Установка параметров шифрования и дешифрования конфигурационной последовательности кристаллов семейств Artix‐7, Kintex‐7 и Virtex‐7, Zynq‐7000 AP SoC

Вид страницы Encryption диалоговой панели Edit Device Properties при использовании ПЛИС серий Artix‑7, Kintex‑7 и Virtex‑7 и программируемых систем на кристалле семейства Zynq‑7000 AP SoC представлен на рис. 1. В разделе Encryption Settings сосредоточены параметры, предоставляющие возможность защиты конфигурационной информации проектируемого устройства в процессе и по окончании ее загрузки в кристалл программируемой логики или расширяемой вычислительной платформы.

Параметр Enable Bitstream Encryption разрешает или запрещает шифрование конфигурационного битового потока. Выпадающий список возможных значений этого параметра содержит два варианта: YES и NO. По умолчанию в качестве значения параметра Enable Bitstream Encryption предлагается вариант NO, при котором шифрование конфигурационной последовательности проектируемого устройства не производится. Для защиты конфигурационной информации от несанкционированного копирования необходимо в поле выбора значения рассматриваемого параметра указать вариант YES.

Значение параметра Select location of encryption key определяет ресурс ПЛИС или программируемой системы на кристалле, который используется для хранения ключей шифрования и дешифрования конфигурационной последовательности разрабатываемого устройства. Список возможных значений этого параметра предлагает два варианта: BBRAM и EFUSE. По умолчанию в поле выбора значения параметра Select location of encryption key представлен вариант BBRAM, при котором ключи шифрования и дешифрования записываются в специальное ОЗУ с дополнительным батарейным питанием Battery-Backed RAM (BBRAM). При выборе варианта EFUSE содержимое ключей, используемых в процессах кодирования и декодирования конфигурационного битового потока разрабатываемого проекта, заносится в одноименный энергонезависимый регистр.

Раздел Key Settings содержит параметры, определяющие значения различных ключей, используемых в процессе шифрования и дешифрования конфигурационной информации. С помощью параметра HMAC authentication key задается идентификационный ключ, используемый в процессе аутентификации конфигурационной последовательности в соответствии с алгоритмом HMAC. Идентификационный код указывается с помощью клавиатуры в поле редактирования значения этого параметра в виде последовательности шестнадцатеричных символов.

Значение параметра AES encryption key (key0) определяет код ключа, применяемого в процессах шифрования и дешифрования конфигурационного битового потока разрабатываемого проекта, осуществляемого в соответствии с алгоритмом AES. Этот ключ представляет собой последовательность, состоящую из 256 бит данных, задаваемую обычно в шестнадцатеричном формате. Необходимая последовательность из 64 шестнадцатеричных символов задается с помощью клавиатуры в поле редактирования значения параметра AES encryption key после его активизации. По умолчанию значение ключа AES encryption key не определено (поле редактирования значения одноименного параметра пусто). При этом средства формирования файла конфигурационной последовательности автоматически выбирают эти значения на основании внутренних алгоритмов.

С помощью параметра Input encryption file можно указать идентификатор и расположение на диске файла, в котором хранятся данные, определяющие ключи шифрования и дешифрования для конфигурационной последовательности разрабатываемого устройства. Для таких файлов обычно предусмотрено расширение nky. Название файла, включая полный путь доступа к нему, можно ввести на клавиатуре непосредственно в поле редактирования значения параметра Input encryption file, которое активизируется щелчком левой кнопки мыши при расположении курсора в этом поле. Кроме того, выбрать требуемый каталог и файл можно, используя стандартную панель открытия файла, которая выводится при нажатии клавиши с пиктограммой в виде многоточия («…»), расположенной справа от поля редактирования значения параметра Input encryption file.

Параметр Starting cipher block chaining (CBC) value предоставляет возможность определения начального блока шифрования CBC (Cipher Block Chaining). Ввод значения этого параметра осуществляется с помощью клавиатуры после активизации соответствующего поля редактирования. По умолчанию значение параметра Starting cipher block chaining (CBC) value не определено и назначается средствами генерации файла конфигурационной последовательности автоматически.

При реализации проектируемого устройства на базе кристаллов программируемой логики или расширяемых процессорных платформ серий UltraScale и UltraScale+ страница Encryption диалоговой панели Edit Device Properties имеет вид, приведенный на рис. 2. Раздел Encryption Settings кроме параметров Enable Bitstream Encryption и Select location of encryption key, представленных выше, содержит параметр Enable obfuscated key load, определяющий способ записи ключа шифрования в ОЗУ с дополнительным батарейным питанием BBRAM. Выпадающий список возможных значений этого параметра включает два варианта: ENABLE и DISABLE. При выборе варианта ENABLE перед загрузкой в ОЗУ BBRAM-ключа, предназначенного для шифрования и дешифрования конфигурационной последовательности, производится его кодирование. В случае использования варианта DISABLE, предлагаемого по умолчанию для параметра Enable obfuscated key load, указанный ключ записывается в ОЗУ с дополнительным батарейным питанием без каких-либо изменений.

Рис. 2. Установка параметров шифрования и дешифрования конфигурационной последовательности кристаллов серий UltraScale и UltraScale+

При формировании конфигурационной последовательности для ПЛИС или программируемых систем на кристалле серий UltraScale и UltraScale+ раздел Key Settings содержит пять дополнительных параметров, назначение которых рассматривается ниже.

С помощью параметра Starting AES encryption key (key0) указывается ключ, с которого начинается процесс шифрования или дешифрования конфигурационной последовательности в соответствии с алгоритмом AES-GCM.

Значение параметра Number of encryption blocks per key устанавливает количество 128‑битовых блоков, для кодирования и декодирования которых используется один ключ. Этот параметр может принимать значения в диапазоне 4–2147483647. По умолчанию в поле выбора значения параметра Number of encryption blocks per key представлен вариант 32.

Параметр Number of frames per AES‑256 key определяет число фреймов, которое должно использоваться для любого ключа шифрования в том случае, когда задан ключ идентификации RSA Public Key Authentication. Для этого параметра могут указываться целочисленные значения в интервале 8–2147483647. По умолчанию в поле выбора значения параметра Number of frames per AES‑256 key предлагается вариант 8.

С помощью параметра Starting AES initial vector (IV0) value назначается вектор инициализации для первого ключа шифрования или дешифрования конфигурационной информации в соответствии с алгоритмом AES-GCM.

Значение параметра Starting obfuscate initial vector (Obfuscate IV0) value позволяет указать вектор инициализации для кодированного ключа шифрования.

Параметры управления процедурой аутентификации конфигурационной последовательности кристаллов программируемой логики и расширяемых процессорных платформ серий UltraScale и UltraScale+ представлены на странице Authentication диалоговой панели Edit Device Properties, чей вид изображен на рис. 3. Указанная страница присутствует в диалоговой панели параметров конфигурирования только при выборе для реализации разрабатываемого проекта ПЛИС или программируемых систем на кристалле указанных серий.

Рис. 3. Установка параметров аутентификации конфигурационной последовательности для кристаллов серий UltraScale и UltraScale+

Параметр Enable Bitstream Authentication позволяет выбрать алгоритм аутентификации конфигурационной последовательности проектируемого устройства. Выпадающий список возможных значений этого параметра содержит два варианта: YES и NO. Для разрешения выполнения аутентификации конфигурационной информации в соответствии с алгоритмом RSA необходимо в поле выбора значения параметра Enable Bitstream Authentication указать вариант YES. По умолчанию для этого параметра предлагается вариант NO, при котором процедура аутентификации конфигурационной последовательности осуществляется алгоритмом AES-GCM.

С помощью параметра Input file containing RSA Private Key указывается файл, содержащий ключи идентификации, используемые при аутентификации конфигурационной информации в соответствии с алгоритмом RSA. Идентификатор файла может быть указан на клавиатуре непосредственно в поле редактирования значения этого параметра после его активизации. Более наглядный способ выбора файла предоставляет клавиша с пиктограммой в виде многоточия, расположенная справа от поля редактирования значения параметра Input file containing RSA Private Key. При нажатии на нее появляется диалоговая панель открытия файла, позволяющая быстро найти требуемый файл, как показано на рис. 3.

После определения параметров шифрования и дешифрования конфигурационной последовательности проектируемого устройства рекомендуется установить требуемые опции частичного реконфигурирования и обратного считывания конфигурационных данных из кристалла программируемой логики или расширяемой процессорной платформы.

Установка параметров частичного реконфигурирования и обратного чтения конфигурационных данных

Для установки нужных значений параметров, используемых в процессе частичного реконфигурирования и обратного считывания конфигурационных данных из кристаллов программируемой логики или расширяемых процессорных платформ, следует открыть страницу Readback диалоговой панели Edit Device Properties, как демонстрирует рис. 4.

Рис. 4. Установка параметров частичного реконфигурирования и обратного считывания конфигурационных данных ПЛИС или программируемой системы на кристалле

Параметр Prevent the assertions of GHIGH and GSR during configuration предоставляет возможность блокировки изменения состояния сигналов GHIGH и GSR при осуществлении процесса конфигурирования ПЛИС или программируемой системы на кристалле. Такая блокировка требуется для расширения возможностей частичного реконфигурирования кристаллов программируемой логики или расширяемых процессорных платформ. В выпадающем списке возможных значений этого параметра представлены два варианта: YES и NO. По умолчанию в поле выбора значения параметра Prevent the assertions of GHIGH and GSR during configuration предлагается вариант NO, при котором отсутствует блокировка переключения указанных сигналов. Для установки запрета изменения состояния сигналов GHIGH и GSR в процессе конфигурирования необходимо для параметра Prevent the assertions of GHIGH and GSR during configuration выбрать вариант YES.

Значение параметра Select between the top and bottom ICAP позволяет указать, какой порт внутреннего конфигурационного интерфейса может использоваться при частичном реконфигурировании и обратном считывании конфигурационной информации ПЛИС или программируемой системы на кристалле. Порт ICAP (Internal Configuration Access Port) обеспечивает доступ к конфигурационным регистрам кристалла программируемой логики или расширяемой процессорной платформы. Выпадающий список возможных значений этого параметра содержит три варианта: Auto, Top и Bottom. По умолчанию для параметра Select between the top and bottom ICAP предлагается вариант Auto, разрешающий автоматический выбор порта внутреннего конфигурационного интерфейса. Варианты Top и Bottom предназначены для активизации соответственно верхнего и нижнего портов ICAP.

С помощью параметра Specify security level for Readback and Reconfiguration осуществляется выбор уровня устанавливаемой защиты конфигурационных данных проектируемого устройства, загруженных в кристалл программируемой логики или расширяемой процессорной платформы. Выпадающий список возможных значений этого параметра содержит три варианта: None, Level1 и Level2. Вариант None, предлагаемый по умолчанию, разрешает обратное считывание загруженной конфигурационной последовательности и реконфигурирование ПЛИС или программируемой системы на кристалле. Выбор варианта Level1 запрещает чтение конфигурационных данных из кристалла программируемой логики или расширяемой процессорной платформы. Значение Level2 устанавливает защиту от считывания конфигурационной последовательности проектируемого устройства и реконфигурирования ПЛИС или программируемой системы на кристалле.

Параметр Enable the XADC from continuing to work during partial reconfiguration предназначен для выбора режима функционирования аналого-цифрового блока XADC кристаллов программируемой логики или расширяемых процессорных платформ в процессе выполнения частичного реконфигурирования. Выпадающий список возможных значений этого параметра имеет два варианта: ENABLE и DISABLE. По умолчанию в поле выбора значения параметра Enable the XADC from continuing to work during partial reconfiguration представлен вариант DISABLE, при котором блок XADC при осуществлении частичного реконфигурирования ПЛИС или программируемой системы на кристалле может работать в непрерывном режиме. В случае выбора варианта ENABLE аналого-цифровой блок во время частичного реконфигурирования кристалла функционирует в безопасном режиме.

Установив требуемые значения параметров процесса генерации конфигурационной последовательности и конфигурирования кристалла программируемой логики или расширяемой процессорной платформы, необходимо подтвердить их нажатием клавиши ОК, расположенной в нижней части диалоговой панели Edit Device Properties (рис. 4). После этого надо активизировать процесс формирования конфигурационной последовательности проектируемого устройства.

Формирование конфигурационной последовательности проектируемого устройства

Активизация процесса формирования файла конфигурирования ПЛИС или программируемой системы на кристалле выполняется командой Generate Bitstream, которая одновременно представлена в разделе Program and Debug панели управления Flow Navigator основного окна интегрированной среды разработки Vivado IDE и всплывающем меню Flow. При выборе указанной команды на экране появляется информационная панель с заголовком Generate Bitstream, как показано на рис. 5. В этой информационной панели отображаются краткие сведения о ходе выполнения генерации конфигурационной последовательности проектируемого устройства. В случае возникновения каких-либо ошибок в этом процессе после его аварийного завершения на экран выводится диалоговая панель с заголовком Bitstream Generation Failed, чей вид изображен на рис. 5. Указанная диалоговая панель содержит индикатор состояния параметра View Log, который по умолчанию установлен в положение «Включено». При нажатии клавиши OK, представленной в нижней части диалоговой панели Bitstream Generation Failed, в консольной области основного окна управляющей оболочки САПР серии Xilinx Vivado HLx Design Suite открывается вкладка Log, содержащая подробную информацию о процессе формирования конфигурационной последовательности проектируемого устройства и ошибках, возникших при его выполнении.

Рис. 5. Запуск и аварийное завершение процесса формирования конфигурационной последовательности проектируемого устройства

После успешного завершения рассматриваемого процесса создается файл конфигурационного битового потока, имеющий расширение bit, который можно непосредственно использовать для загрузки в кристалл программируемой логики или расширяемой процессорной платформы, и открывается диалоговая панель с заголовком Bitstream Generation Completed, чей вид приведен на рис. 6.

Рис. 6. Активизация и успешное завершение процесса генерации конфигурационной последовательности проектируемого устройства

Открывшаяся диалоговая панель содержит группу кнопок с зависимой фиксацией, которые позволяют выбрать дальнейшие действия в процессе проектирования разрабатываемого устройства. Если необходимо вновь открыть базу данных проекта, реализованного в ПЛИС или программируемой системе на кристалле, следует зафиксировать в нажатом состоянии кнопку Open Implemented Design. Для получения быстрого доступа к отчету о ходе и результатах выполнения генерации конфигурационной последовательности проектируемого устройства необходимо переключить в нажатое положение кнопку View Reports. Чтобы перейти к очередному обязательному этапу проектирования (процессу загрузки конфигурационной последовательности в кристалл программируемой логики или расширяемой процессорной платформы), нужно установить в нажатое состояние кнопку Open Hardware Manager. Для формирования файлов программирования конфигурационного ППЗУ необходимо зафиксировать в нажатом положении кнопку Generate Memory Configuration File. Выбрав требуемый вариант дальнейших действий, следует подтвердить его нажатием клавиши OK, находящейся в нижней части диалоговой панели Bitstream Generation Completed.

Прежде чем перейти к следующему обязательному этапу проектирования разрабатываемого устройства, целесообразно ознакомиться с отчетом о ходе и результатах выполнения процесса генерации конфигурационной последовательности. Поэтому в рассматриваемой диалоговой панели следует переключить в нажатое положение кнопку View Reports, как показано на рис. 6. При этом после нажатия клавиши OK в диалоговой панели Bitstream Generation Completed в консольной области основного окна интегрированной среды разработки Vivado IDE открывается вкладка Reports, которая содержит таблицу всех доступных отчетов, сформированных на различных этапах проектирования.

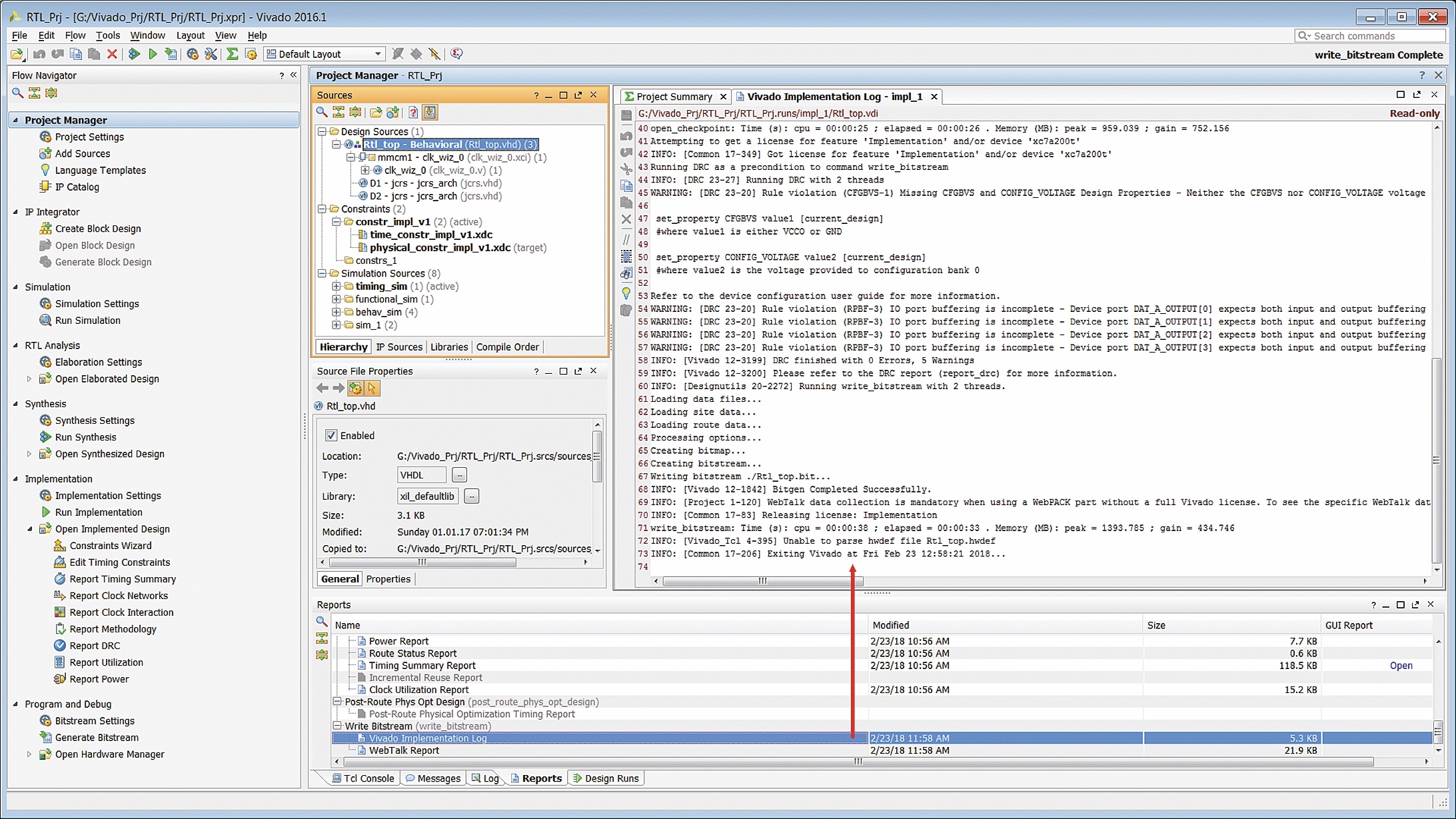

Информация о выполнении этапа генерации конфигурационного битового потока записывается в конец документа, содержащего отчет о результатах процесса реализации проектируемого устройства в кристалле программируемой логики или расширяемой процессорной платформы. Поэтому для отображения отчета о ходе и результатах процесса формирования конфигурационной последовательности следует расположить курсор в строке Vivado Implementation Log, представленной в разделе Write Bitstream, и дважды щелкнуть левой кнопкой мыши. После этого в рабочей области основного окна управляющей оболочки САПР серии Xilinx Vivado HLx Design Suite появляется новая вкладка встроенного текстового редактора с названием Vivado Implementation Log — <идентификатор_процесса_реализации>, которая включает текст сформированного отчета (рис. 7).

Рис. 7. Отображение отчета о выполнении этапа генерации конфигурационной последовательности проектируемого устройства

Сгенерированная конфигурационная последовательность проектируемого устройства может быть загружена непосредственно в ПЛИС или программируемую систему на кристалле или использована для формирования файла программирования ППЗУ. Процедура загрузки конфигурационного битового потока в кристалл программируемой логики или расширяемой процессорной платформы не является обязательной. Она предназначена в основном для проверки функционирования проектируемого устройства на аппаратном уровне, которую целесообразно выполнять перед программированием конфигурационного ППЗУ. Для осуществления процесса загрузки конфигурационной последовательности из файла с расширением bit в ПЛИС или программируемую систему на кристалле применяется режим периферийного сканирования JTAG/Boundary-Scan Configuration. При использовании этого режима перед формированием конфигурационной последовательности необходимо указать для параметра Select Startup Clock вариант JTAGCLK [40].

Подключение загрузочного кабеля для конфигурирования кристалла программируемой логики или расширяемой процессорной платформы в режиме периферийного сканирования

Запись конфигурационной информации в кристалл программируемой логики или расширяемой процессорной платформы в САПР серии Xilinx Vivado HLx Design Suite осуществляется с помощью специального кабеля, подключаемого к порту JTAG-интерфейса. Рассматриваемые средства проектирования поддерживают следующие типы загрузочных кабелей фирмы Xilinx, которые выпускались в различное время:

- загрузочный кабель Platform Cable USB (DLC9G, DLC9LP, DLC9);

- загрузочный кабель Platform Cable USB II (DLC10).

В настоящее время фирмой Xilinx предоставляется только загрузочный кабель последнего типа. Кроме того, для конфигурирования кристаллов программируемой логики и расширяемых вычислительных платформ фирмы Xilinx можно использовать инструментальные средства загрузки, производимые третьими фирмами, например компанией Digilent Incorporated. Аппаратные загрузочные средства, выпускаемые этой компанией, отличаются низкой стоимостью и компактностью. Средствами конфигурирования ПЛИС и программируемых систем на кристалле, представленными в составе САПР серии Xilinx Vivado HLx Design Suite, поддерживаются следующие инструменты загрузки компании Digilent Incorporated:

- загрузочный кабель JTAG HS1 Programming Cable for Xilinx FPGAs;

- загрузочный кабель JTAG-HS2 Programming Cable for Xilinx FPGAs;

- загрузочный кабель JTAG-HS3 Programming Cable for Xilinx FPGAs;

- встраиваемый загрузочный модуль JTAG-SMT1;

- встраиваемый загрузочный модуль JTAG-SMT2.

На сегодня из перечисленных вариантов инструментальных средств конфигурирования кристаллов программируемой логики и расширяемых процессорных платформ фирмы Xilinx, производимых компанией Digilent Incorporated, актуальными являются загрузочный кабель JTAG-HS3 Programming Cable for Xilinx FPGAs и встраиваемый загрузочный модуль JTAG-SMT2.

Процедура верификации разрабатываемого устройства на аппаратном уровне начинается с подключения загрузочного кабеля одного из рассмотренных типов к соответствующему USB-порту компьютера, на котором установлена САПР серии Xilinx Vivado HLx Design Suite, и разъему JTAG-интерфейса инструментального модуля, используемого для аппаратной отладки или реализации разрабатываемого устройства. При этом нужно убедиться, что сигнальные выводы загрузочного кабеля Test Data In (TDI), Test Mode Select (TMS), Test Clock (TCK) и Test Data Out (TDO) подключены к одноименным контактам кристалла, а выводы GND и VCC — к общей шине и цепи питания. После присоединения инструментальных средств загрузки к разъемам ПК и отладочной платы следует подать напряжение питания на используемый аппаратный модуль, а затем активизировать средства конфигурирования ПЛИС и программируемых систем на кристалле, входящие в состав САПР серии Xilinx Vivado HLx Design Suite.

Активизация средств конфигурирования

Для активизации средств конфигурирования кристаллов программируемой логики и расширяемых процессорных платформ, представленных в составе САПР серии Xilinx Vivado HLx Design Suite, необходимо воспользоваться командой Open Hardware Manager. Доступ к указанной команде предоставляет раздел Program and Debug панели управления Flow Navigator основного окна интегрированной среды разработки Vivado IDE и всплывающее меню Flow, как демонстрирует рис. 8.

Рис. 8. Активизация средств конфигурирования кристаллов программируемой логики и расширяемых процессорных платформ

После выполнения команды Open Hardware Manager основное окно управляющей оболочки САПР серии Xilinx Vivado HLx Design Suite преобразуется к виду, приведенному на рис. 8. В разделе Program and Debug панели управления Flow Navigator открывается подраздел Hardware Manager, предоставляющий быстрый доступ к основным операциям, необходимым для конфигурирования ПЛИС или программируемой системы на кристалле. В области окон данных открывается встроенное окно Hardware, предназначенное для отображения сведений об инструментальных средствах, которые могут использоваться для загрузки конфигурационной последовательности проектируемого устройства и его аппаратной отладки. Первоначально это окно не содержит никакой информации.

Для получения сведений о доступных инструментальных средствах рекомендуется воспользоваться процедурой автоматического обнаружения подключенного оборудования, которая запускается с помощью команды Auto Connect. Она имеется во всплывающем меню Tools основного окна интегрированной среды разработки Vivado IDE. Кроме того, команду Auto Connect содержат всплывающие меню, открываемые при выборе команды Open Target, представленной в подразделе Hardware Manager панели управления Flow Navigator и верхней части встроенного окна Hardware (рис. 9). При выполнении указанной команды на экране появляется информационная панель Auto Connect, где отображаются краткие сведения о ходе процедуры автоматического обнаружения подключенного оборудования, доступного для загрузки конфигурационной последовательности проектируемого устройства в кристалл программируемой логики и расширяемой процессорной платформы. Более подробная информация о выполнении этой процедуры приводится на вкладке TCL Console консольной области основного окна управляющей оболочки САПР серии Xilinx Vivado HLx Design Suite.

Рис. 9. Запуск процедуры автоматического обнаружения подключенного оборудования, доступного для загрузки конфигурационной последовательности

После успешного завершения процедуры автоматического обнаружения подключенного оборудования основное окно интегрированной среды разработки Vivado IDE приобретает вид, изображенный на рис. 10.

Рис. 10. Вид основного окна интегрированной среды разработки Vivado IDE после успешного завершения процедуры автоматического обнаружения подключенного оборудования

Если в результате выполнения рассмотренной процедуры не удалось корректно идентифицировать инструментальные средства, используемые для загрузки конфигурационной последовательности проектируемого устройства, то следует воспользоваться мастером подключения нового оборудования Open New Hardware Target Wizard. Активизация этого мастера осуществляется командой Open New Target, доступ к которой предоставляет всплывающее меню Tools основного окна интегрированной среды разработки Vivado IDE. Указанная команда может быть выбрана также во всплывающем меню, которое открывается щелчком левой кнопки мыши при расположении курсора в строке Open Target, представленной в подразделе Hardware Manager панели управления Flow Navigator и верхней части встроенного окна Hardware (рис. 11).

После выбора команды Open New Target на экране появляется стартовая информационная панель мастера подключения нового оборудования, применяемого для загрузки конфигурационной последовательности разрабатываемого проекта. Эта панель с заголовком Open Hardware Target, чей вид приведен на рис. 11, содержит краткие сведения об исходных данных для подключения используемого оборудования. Ознакомившись с представленной информацией, нужно нажатием клавиши Next, расположенной в нижней части стартовой панели, перейти ко второй диалоговой панели мастера Open New Hardware Target Wizard, чей вид изображен на рис. 12.

Рис. 12. Выбор типа сервера для подключения оборудования, применяемого для загрузки конфигурационной последовательности

Эта диалоговая панель, имеющая заголовок Hardware Server Settings, предназначена для выбора типа сервера, используемого для подключения инструментальных средств загрузки конфигурационной последовательности. Требуемый тип сервера указывается в поле выбора значения параметра Connect to, выпадающий список которого содержит два варианта: Local server и Remote server. Если для загрузки конфигурационной последовательности разрабатываемого устройства применяется отладочная плата, подключенная к персональному компьютеру, на котором выполняется процесс проектирования в САПР серии Xilinx Vivado HLx Design Suite, то в поле выбора значения параметра Connect to следует указать вариант Local Server. При использовании аппаратных средств, установленных на удаленном сервере, необходимо выбрать вариант Remote Server. В случае выбора последнего варианта диалоговая панель Hardware Server Settings автоматически преобразуется к виду, представленному на рис. 13.

Рис. 13. Определение основных параметров удаленного сервера для подключения инструментальных средств загрузки конфигурационной последовательности

В поле редактирования значения параметра Host name необходимо с помощью клавиатуры указать идентификатор или IP-адрес удаленного сервера. Номер порта определяется в поле редактирования значения параметра Port. После выбора типа сервера и его основных параметров нужно с помощью клавиши Next перейти к очередной диалоговой панели мастера Open New Hardware Target Wizard, чей вид приведен на рис. 14.

Рис. 14. Выбор инструментальных средств для загрузки конфигурационной последовательности проектируемого устройства

Третья диалоговая панель с заголовком Select Hardware Target предоставляет информацию об аппаратных средствах, подключенных к указанному серверу. Краткие сведения о доступном оборудовании отображаются в таблице Hardware Targets, которая включает в себя три колонки с названиями Type, Name и JTAG Clock Frequency. В колонках Type и Name приведена информация о типе и условном обозначении обнаруженных аппаратных средств. Каждая ячейка колонки JTAG Clock Frequency представляет собой поле выбора значения одноименного параметра. Этот параметр определяет значение частоты тактового сигнала интерфейса JTAG, используемого для конфигурирования ПЛИС или программируемых систем на кристалле. По умолчанию для инструментальных средств конфигурирования кристаллов программируемой логики и расширяемых процессорных платформ фирмы Xilinx, выпускаемых компанией Digilent Incorporated, предлагается значение частоты тактового сигнала интерфейса JTAG, равное 15 МГц. При выборе в выпадающем списке возможных значений параметра JTAG Clock Frequency варианта, отличающегося от установленного по умолчанию, следует убедиться, что ПЛИС или программируемые системы на кристалле, входящие в состав используемого оборудования, поддерживают соответствующую частоту конфигурирования.

В таблице Hardware Targets следует выделить строку, соответствующую инструментальным средствам, используемым для загрузки конфигурационной последовательности проектируемого устройства. При этом в таблице Hardware Devices появится информация о кристаллах программируемой логики и расширяемых процессорных платформ, входящих в состав выбранного оборудования. После определения аппаратных средств для загрузки конфигурационной последовательности проектируемого устройства нужно перейти к заключительной диалоговой панели мастера Open New Hardware Target Wizard. Эта панель, имеющая заголовок Open Hardware Target Summary, содержит информацию об инструментальных средствах, выбранных для аппаратной верификации разрабатываемого проекта (рис. 15).

Рис. 15. Отображение информации об инструментальных средствах, выбранных для аппаратной верификации разрабатываемого проекта

Процесс подключения оборудования, применяемого для загрузки конфигурационной последовательности проектируемого устройства, завершается нажатием клавиши Finish, представленной в нижней части заключительной диалоговой панели мастера Open New Hardware Target Wizard. После этого основное окно интегрированной среды разработки Vivado IDE преобразуется к виду, показанному на рис. 10, позволяющему приступить непосредственно к аппаратной верификации проектируемого устройства.

- Зотов В. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPackISE. М.: Горячая линия — Телеком, 2003.

- Зотов В. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М.: Горячая линия — Телеком, 2006.

- Зотов В. Проектирование встраиваемых микропроцессорных систем на базе расширяемых процессорных платформ семейства Zynq-7000 AP SoC в САПР XilinxISEDesignSuite// Компоненты и технологии. 2014. № 4–12. № 1.

- Зотов В. Моделирование цифровых устройств, проектируемых на основе ПЛИС фирмы Xilinx, средствами ISIM в САПР ISE Design Suite// Компоненты и технологии. 2013. № 2–3.

- Зотов В. Средства автоматизированного проектирования и этапы разработки встраиваемых микропроцессорных систем на базе расширяемых процессорных платформ семейства Zynq-7000 AP SoC // Компоненты и технологии. 2013. № 2–3.

- Зотов В. Особенности архитектуры нового поколения ПЛИС с архитектурой FPGA фирмы Xilinx // Компоненты и технологии. № 12.

- Зотов В. Расширение семейства программируемых систем на кристалле Zynq-7000 AP SoC // Компоненты и технологии. № 12. 2014. № 1.

- Vivado Design Suite User Guide. Release Notes, Installation and Licensing. Xilinx, 2016.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 1 // Компоненты и технологии. 2016. № 7.

- Зотов В. Конвертирование проектов цифровых устройств, разрабатываемых на основе ПЛИС и полностью программируемых систем на кристалле фирмы Xilinx в среде ISEDesignSuite, в формат САПР VivadoDesignSuite// Компоненты и технологии. 2013. № 8–10.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 2 // Компоненты и технологии. 2016. № 8.

- Зотов В. Разработка VHDL-описаний цифровых устройств, проектируемых на основе ПЛИС фирмы Xilinx, с использованием шаблонов САПР ISEDesignSuite // Компоненты и технологии. 2010. № 2–12. 2011. № 1–12. 2012. № 1–12.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 3 // Компоненты и технологии. 2016. № 9.

- Vivado Design Suite User Guide. Using Constraints. Xilinx, 2016.

- Vivado Design Suite Properties Reference Guide. Xilinx, 2016.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 4 // Компоненты и технологии. 2016. № 10.

- Зотов В. Проектирование узлов синхронизации цифровых устройств и встраиваемых микропроцессорных систем, реализуемых на базе ПЛИС фирмы Xilinx серий Artix-7, Kintex-7 и Virtex-7. Часть 1 // Компоненты и технологии. 2016. № 3.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 5 // Компоненты и технологии. 2016. № 11.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 6 // Компоненты и технологии. 2016. № 12.

- Зотов В. ModelSim — система HDL-моделирования цифровых устройств. // Компоненты и технологии. 2002. № 6.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 7 // Компоненты и технологии. 2017. № 1.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 8 // Компоненты и технологии, № 2. 2017.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 9 // Компоненты и технологии. 2017. № 3.

- UltraFast Design Methodology Quick Reference Guide. Xilinx, 2016.

- UltraFast Design Methodology Guide for the Vivado Design Suite. Xilinx, 2016.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 10 // Компоненты и технологии. 2017. № 4.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 11 // Компоненты и технологии. 2017. № 5.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 12 // Компоненты и технологии. 2017. № 6.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 13 // Компоненты и технологии. 2017. № 7.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 14 // Компоненты и технологии. 2017. № 8.

- Vivado Design Suite User Guide: Synthesis. Xilinx, 2016.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 15 // Компонентыитехнологии. 2017. № 9.

- Large FPGA Methodology Guide Including Stacked Silicon Interconnect (SSI) Technology. Xilinx, 2012.

- Santarini M. Stacked & Loaded: Xilinx SSI, 28-Gbps I/O Yield Amazing FPGAs // Xcell Journal. 2011. № 74.

- Santarini M. Xilinx Ships World’s Highest-Capacity FPGA Using SSI Technology // Xcell Journal. 2011. № 77.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinxв САПР серии VivadoHLxDesignSuite. Часть 16 // Компоненты и технологии. 2017. № 10.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии VivadoHLxDesignSuite. Часть 17 // Компоненты и технологии. 2017. № 12.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии Vivado HLx Design Suite. Часть 18 // Компоненты и технологии. 2018. № 1.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии Vivado HLx Design Suite. Часть 19 // Компоненты и технологии. 2018. № 2.

- Зотов В. Проектирование цифровых устройств на базе ПЛИС фирмы Xilinx в САПР серии Vivado HLx Design Suite. Часть 20 // Компоненты и технологии. 2018. № 3.

4 августа, 2020

4 августа, 2020 20 августа, 2020

20 августа, 2020 25 октября, 2021

25 октября, 2021