Проектирование КИХ-фильтров в системе Xilinx System Generator с применением методологии Black Boxes

Импорт проектов, созданных в САПР ПЛИС Xilinx ISE Design Suite с использованием единственных VHDL-файлов

В Xilinx System Generator проанализируем проектирование КИХ-фильтра на четыре отвода у = С0x0+C1x1+C2x2+C3x3 с заданными коэффициентами С0 = –2, C1 = –1, C2 = 7 и C3 = 6 [1, 2, 3, 4] с применением методологии Black Boxes. Рассмотрим случай, когда на вход фильтра поступает сигнал –5, 3, 1, 0, 0 и 0 т. д. Правильные значения на выходе фильтра: 10, –1, –40, –10, 25, 6 и 0 т. д.

Пример 1 демонстрирует нижний уровень иерархии проекта КИХ-фильтра на четыре отвода, созданного с использованием единственного VHDL-файла. Верхним уровнем иерархии является схемный файл fir.sch, состоящий из символа с именем fir4 и портов (не показан). Испытательный стенд сформируем в ручном режиме.

Согласно рекомендациям Xilinx для эффективного использования DSP-блоков ПЛИС необходим сигнал синхронного сброса (активным является сигнал низкого уровня). Выражение для выходного сигнала фильтра также должно использовать тактовый сигнал.

В данном примере для преобразования типов применен пакет std_logic_arith библиотеки IEEE (также возможно использование пакета numeric_std). Переменные pro и acc представлены в 8‑ и 10‑разрядном дополнительном двоичном коде (знаковый тип signed). Поскольку порты date и q_reg относятся к типу std_logic_vector, то необходимо осуществить преобразование типов с помощью следующих функций: conv_signed(conv_integer(date),4) для сигнала date и std_logic_vector(acc) для сигнала q_reg. Функция conv_integer(date) преобразует сигнал date в целое десятичное число с учетом знака, а функция conv_signed преобразует в 4‑разрядный дополнительный двоичный код. Для линии задержки, организованной на переменной shift, формируется тип shift_arr (массив из четырех 4‑разрядных двоичных слов), заданный пользователем.

library ieee;

use ieee.std_ogic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

package coeffs is

type coef_arr is array (0 to 3) of signed(3 downto 0);

constant coefs: coef_arr:= coef_arr'("1110", "1111", "0111", "0110");

end coeffs;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

use work.coeffs.all;

entity fir4 is

port (clk, reset, ce: in std_logic;

date: in std_logic_vector(3 downto 0);

q_reg: out std_logic_vector (9 downto 0));

end fir4;

architecture beh of fir4 is

begin

process(clk,reset,ce,date)

type shift_arr is array (3 downto 0) of signed (3 downto 0);

variable shift: shift_arr;

variable pro: signed(7 downto 0);

variable acc: signed (9 downto 0);

begin

q_reg<= (others => '0');

if(clk'event and clk = '1') then

if reset='0' then

for i in 0 to 3 loop

shift(i):= (others => '0');

end loop;

elsif ce='1' then

shift(0):=conv_signed(conv_integer(date),4);

pro := shift(0) * coefs(0);

acc := conv_signed(pro, 10);

for i in 2 downto 0 loop

pro := shift(i+1) * coefs(i+1);

acc := acc + conv_signed(pro, 10);

shift(i+1):= shift(i);

end loop;

end if;

end if;

q_reg<=std_logic_vector(acc);

end process;

end beh;

Пример 1. Код языка VHDL КИХ-фильтра на четыре отвода

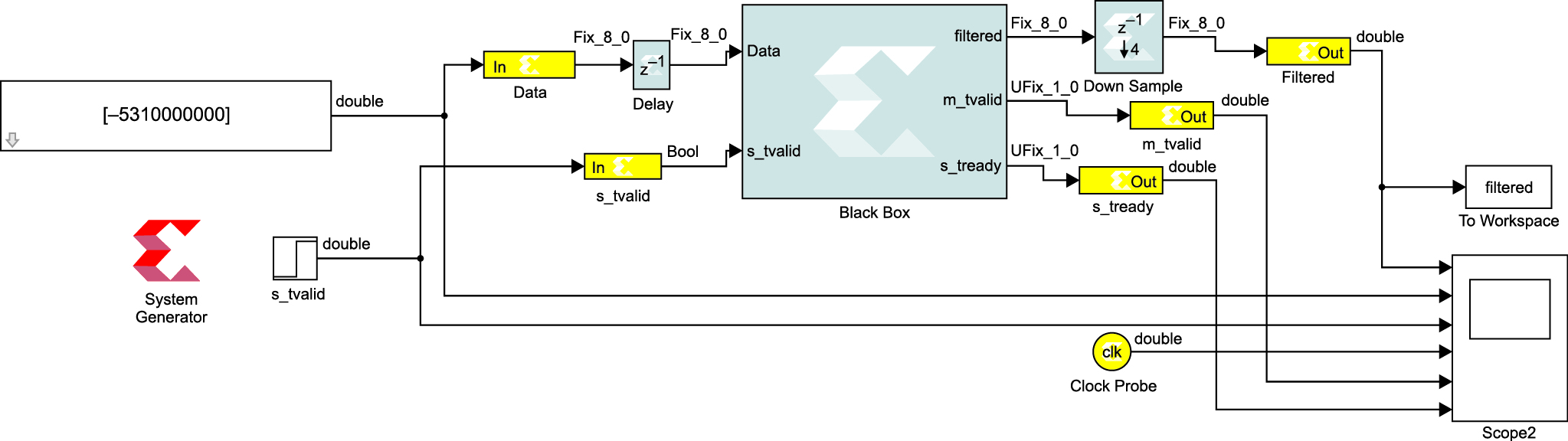

Убедившись с помощью испытательного стенда в том, что код языка VHDL КИХ-фильтра на четыре отвода работает корректно, перейдем к разработке имитационной модели. На рис. 1 показана имитационная модель КИХ-фильтра на четыре отвода для реализации в базисе ПЛИС серии Spartan‑6 xa6slx4-3tqg144 на основе функционального блока Black Box. Настройки маркера System Generator следующие: период синхросигнала 100 нс, период симуляции в Simulink 1 с.

Рис. 1. Имитационная модель КИХ-фильтра на четыре отвода для реализации в базисе ПЛИС серии Spartan 6 xa6slx4-3tqg144 на основе функционального блока Black Box

Для того чтобы воспользоваться данной методологией, необходимо из библиотеки Xilinx System Generator добавить в разрабатываемую модель фильтра функциональный блок Black Box и указать на VHDL-файл с именем fir4 (пример 1), а также подключить симулятор ISE (рис. 2). В автоматическом режиме будет создан m‑файл (m‑функция КИХ-фильтра) системы Matlab с именем fir4_config. Более подробную информацию о структуре m‑файлов, генерируемых Xilinx System Generator, можно посмотреть в работе [5].

Рис. 2. Настройки функционального блока Black Box. Будет сформирован m файл с именем fir4_config, задано функциональное моделирование в ISE

С учетом того что современные ПЛИС построены на основе методологии синхронного проектирования, необходимо с помощью следующей конструкции в коде языка VHDL для последовательностных устройств обеспечить связку синхросигнала clk и сигнала разрешения его подачи ce [6]:

elsif (clk'event and clk='1') then if (ce = '1') then ….

При этом на функциональном блоке Black Boxes сигналы clk и ce не отображаются. m‑файл fir4_config системы Matlab является редактируемым. Например, по умолчанию результат фильтрации на шине q_reg представляется в формате с фиксированной запятой для беззнаковых чисел как ‘UFix_10_0’. Поскольку коэффициенты фильтра и входные отсчеты могут быть как со знаком, так и без, необходимо отредактировать формат представления профильтрованного сигнала Sout с ‘UFix_10_0’ на ‘Fix_10_0’. В дальнейшем это придется делать для всех рассматриваемых примеров.

Анализируя m‑файл, видим, что сформировался фильтр типа Single-Rate FIR (входная частота дискретизации fclk равна выходной частоте дискретизации, то есть изменение частоты дискретизации не происходит; такие фильтры получили название «односкоростные фильтры»), функция setup_as_single_rate(block, clkname, cename). Частота дискретизации определяется как fclk/N для несимметричного и как fclk/N+1 для симметричного фильтра, где fclk — частота тактирования ядра фильтра; N‑разрядность входной шины данных (точность представления входных значений, подлежащих фильтрации).

function fir4_config(this_block)

this_block.setTopLevelLanguage('VHDL');

this_block.setEntityName('fir4');

% System Generator has to assume that your entity has a combinational feed through;

% if it doesn't, then comment out the following line:

this_block.tagAsCombinational;

this_block.addSimulinkInport('reset');

this_block.addSimulinkInport('date');

this_block.addSimulinkOutport('q_reg');

q_reg_port = this_block.port('q_reg');

q_reg_port.setType('Fix_10_0');

% -----------------------------

if (this_block.inputTypesKnown)

% do input type checking, dynamic output type and generic setup in this code block.

if (this_block.port('reset').width ~= 1);

this_block.setError('Input data type for port "reset" must have width=1.');

end

this_block.port('reset').useHDLVector(false);

if (this_block.port('date').width ~= 4);

this_block.setError('Input data type for port "date" must have width=4.');

end

end % if(inputTypesKnown)

% -----------------------------

% -----------------------------

if (this_block.inputRatesKnown)

setup_as_single_rate(this_block,'clk','ce')

end % if(inputRatesKnown)

% -----------------------------

% (!) Set the inout port rate to be the same as the first input

% rate. Change the following code if this is untrue.

uniqueInputRates = unique(this_block.getInputRates);

% Add addtional source files as needed.

% |-------------

% | Add files in the order in which they should be compiled.

% | If two files "a.vhd" and "b.vhd" contain the entities

% | entity_a and entity_b, and entity_a contains a

% | component of type entity_b, the correct sequence of

% | addFile() calls would be:

% | this_block.addFile('b.vhd');

% | this_block.addFile('a.vhd');

% |-------------

% this_block.addFile('');

% this_block.addFile('');

this_block.addFile('fir4.vhd');

return;

% ------------------------------------------------------------

function setup_as_single_rate(block,clkname,cename)

inputRates = block.inputRates;

uniqueInputRates = unique(inputRates);

if (length(uniqueInputRates)==1 & uniqueInputRates(1)==Inf)

block.addError('The inputs to this block cannot all be constant.');

return;

end

if (uniqueInputRates(end) == Inf)

hasConstantInput = true;

uniqueInputRates = uniqueInputRates(1:end-1);

end

if (length(uniqueInputRates) ~= 1)

block.addError('The inputs to this block must run at a single rate.');

return;

end

theInputRate = uniqueInputRates(1);

for i = 1:block.numSimulinkOutports

block.outport(i).setRate(theInputRate);

end

block.addClkCEPair(clkname,cename,theInputRate);

return;

% ---------------------------------------------------------

Пример 2. m-файл, генерируемый Xilinx System Generator (с комментариями)

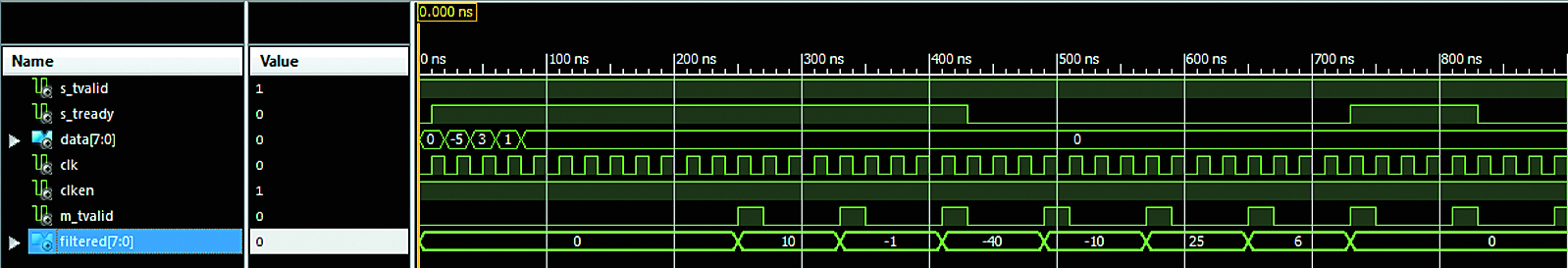

На рис. 3 показаны результаты имитационного моделирования в системе Matlab/Simulink КИХ-фильтра на четыре отвода, а на рис. 4 — функциональное моделирование в САПР ПЛИС Xilinx ISE Design Suite v.14.4 для двух случаев. В первом случае (рис. 4а) проект создан на основе единственного VHDL-файла (пример 1) с ручным формированием испытательного стенда, а во втором (рис. 4б) — оптимизированный VHDL-код с автоматическим формированием испытательного стенда, созданный с помощью маркера Xilinx System Generator. Сравнивая результаты имитационного и функционального (рис. 3, 4) моделирования, видим, что КИХ-фильтр работает корректно. Анализ (рис. 4) показывает, что по коду языка VHDL, приведенному в примере 1, сформировался параллельный КИХ-фильтр. После задержки в четыре такта синхроимпульса результат вычисления уже доступен с приходом нового такта синхроимпульса.

Рис. 3. Имитационное моделирование в системе Matlab/Simulink КИХ-фильтра на четыре отвода, созданного с использованием единственного VHDL-файла

Рис. 4. Функциональное моделирование КИХ-фильтра на четыре отвода в САПР ПЛИС Xilinx ISE Design Suite, созданного:

а) на основе проекта, состоящего из единственного VHDL-файла (пример 1);

б) на основе функционального блока Black Box

На рис. 5 показана верификация двух моделей КИХ-фильтров, разработанных с использованием функционального блока FIR Compiler 6.3 Xilinx System Generator, являющегося аналогом функции FIR Compiler v6.3 САПР Xilinx ISE, получаемой с помощью генератора параметризированных ядер XLogiCORE IP и с применением кода языка VHDL (функциональный блок Black Box).

Рис. 5. Верификация двух имитационных моделей КИХ-фильтров, разработанных с использованием функционального блока FIR Compiler 6.3 и с применением кода языка VHDL (функциональный блок Black Box)

В первом случае функциональный блок FIR Compiler 6.3 настроен на реализацию систолического КИХ-фильтра, являющегося разновидностью параллельных структур.

На рис. 6 представлены результаты имитационного и функционального моделирования двух моделей КИХ-фильтров, разработанных с использованием функционального блока FIR Compiler 6.3 Xilinx System Generator и с применением кода языка VHDL. Для обеих моделей КИХ-фильтров испытательные стенды формируются в автоматическом режиме.

Рис. 6.

а) Имитационное моделирование;

б) функциональное моделирование двух моделей КИХ-фильтров, разработанных с использованием функционального блока FIR Compiler 6.3 Xilinx System Generator и с применением кода языка VHDL (функциональный блок Black Box)

Анализ рис. 6 показывает, что КИХ-фильтр на основе систолической структуры характеризуется значительно большей латентностью появления профильтрованного сигнала (start-up latency) на выходе [2]. Во втором случае при синтезе кода по единственному VHDL-файлу формируется фильтр с наименьшей латентностью (рис. 6). Временные диаграммы работы характерны для параллельных структур КИХ-фильтров.

Оценка ресурсов ПЛИС серии Spartan‑6 xa6slx4-3tqg144 при реализации КИХ-фильтров на четыре отвода различными способами представлена в таблице. Из таблицы видно, что наибольшим быстродействием обладают проекты, созданные с использованием либо генератора параметризированных ядер XLogiCORE IP, либо функциональных блоков Xilinx System Generator. Имитационная модель, созданная в Simulink с применением Xilinx System Generator и функционального блока Black Boxes, основанная на импорте VHDL-файла, показывает наихудшее быстродействие, но обеспечивает сбалансированное использование логических ресурсов (в сторону уменьшения) и ЦОС-блоков ПЛИС.

|

Ресурсы ПЛИС |

Параллельные структуры фильтров |

Последовательная структура фильтра |

||

|

Имитационная модель в Simulink, Xilinx System Generator с применением Black Boxes (пример 1) |

Проект в САПР ПЛИС Xilinx ISE Design Suite с применением функции FIR Compiler v6.3 и генератора XLogiCORE IP (рис. 1) [2] |

Имитационная модель в Simulink, Xilinx System Generator с применением функционального блока FIR Compiler 6.3 (рис. 4) [3] |

Имитационная модель в Simulink, Xilinx System Generator, Dual Port Memory MAC FIR Filter, 1 МАС—блок [4] |

|

|

Максимальная частота, МГц (на этапе Post-Map) |

114 |

334 |

305 |

279 |

|

Число ЦОС-блоков DSP-48A |

3 |

1 |

4 |

1 |

|

Триггеров |

8 |

48 |

91 |

57 |

|

Секций с LUT |

6 |

33 |

56 |

38 |

|

Точность представления входного и профильтрованного сигнала, бит |

FIX_4_0 и FIX_10_0 |

4 и 8 |

FIX_8_0 и FIX_20_8 |

FIX_4_0 и FIX_10_0 |

Примечание. Коэффициенты фильтра представлены с 4‑битной точностью.

Импорт проектов, созданных в САПР ПЛИС Xilinx ISE Design Suite с использованием структурного стиля языка VHDL

Проект будет состоять из двух VHDL-фай-лов — низкого (файл fir4) и верхнего уровней иерархии (fir). Файл верхнего уровня иерархии fir получим путем пересохранения файла fir.vhf, который извлекается из проекта (пример 1) в автоматическом режиме (HDL Functional Model) в файл fir.vhd (пример 3).

library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; library UNISIM; use UNISIM.Vcomponents.ALL; entity fir is port ( ce : in std_logic; clk : in std_logic; date : in std_logic_vector (3 downto 0); reset : in std_logic; filtered : out std_logic_vector (9 downto 0)); end fir; architecture BEHAVIORAL of fir is component fir4 port ( clk : in std_logic; reset : in std_logic; ce : in std_logic; date : in std_logic_vector (3 downto 0); q_reg : out std_logic_vector (9 downto 0)); end component; begin XLXI_1 : fir4 port map (ce=>ce, clk=>clk, date(3 downto 0)=>date(3 downto 0), reset=>reset, q_reg(9 downto 0)=>filtered(9 downto 0)); end BEHAVIORAL; Пример 3. Структурное описание КИХ-фильтра на четыре отвода (файл верхнего уровня иерархии)

C помощью функционального блока Black Box создадим m‑файл с именем fir_config (пример 4), указав на файл верхнего уровня иерархии fir.vhd (рис. 7). Рис. 1 и рис. 7 внешне схожи, за исключением имен портов, которые на рис. 7 соответствуют именам портов объекта fir (пример 3).

Рис. 7. Имитационная модель КИХ-фильтра на четыре отвода для реализации в базисе ПЛИС серии Spartan 6 xa6slx4-3tqg144 на основе функционального блока Black Box c использованием структурного стиля языка VHDL. m файл с именем fir_config будет создан на основе файла верхнего уровня иерархии fir.vhd

function fir_config(this_block)

this_block.setTopLevelLanguage('VHDL');

this_block.setEntityName('fir');

this_block.tagAsCombinational;

this_block.addSimulinkInport('date');

this_block.addSimulinkInport('reset');

this_block.addSimulinkOutport('filtered');

filtered_port = this_block.port('filtered');

filtered_port.setType('Fix_10_0');

…..

this_block.addFile('fir4.vhd');

this_block.addFile('fir.vhd');

return;

Пример 4. Фрагмент m-файла, генерируемого Xilinx System Generator, с учетом использования структурного стиля языка VHDL

Пример 4 показывает, что необходимо отредактировать формат представления профильтрованного сигнала filtered с ‘UFix_10_0’ на ‘Fix_10_0’ и указать путь на файл низкого уровня иерархии fir4.vhd.

Импорт проектов, созданных в САПР ПЛИС Xilinx ISE Design Suite с использованием библиотечных элементов языка VHDL

В этом разделе также применен структурный стиль языка VHDL. Рассмотрим вариант разработки имитационной модели КИХ-фильтра с помощью библиотечных элементов (пример 5). На рис. 8а показана иерархия проекта, состоящая из файла верхнего уровня иерархии fir.vhd и файла низкого уровня fir4.vhd, а на рис. 8б показано, что файл fir4.vhd размещен в дополнительно созданную библиотеку fir_lib, файлы fir.vhd и test.vhd (пример 6) размещаются в библиотеку work. Пример 7 демонстрирует фрагмент изменений, которые необходимо внести в m‑файл fir_config, генерируемый Xilinx System Generator.

Рис. 8.

а) Иерархия проекта КИХ-фильтра, состоящая из файла верхнего уровня иерархии fir.vhd и файла низкого уровня fir4.vhd;

б) файл fir4.vhd размещен в библиотеку fir_lib, а файлы fir4.vhd и test.vhd размещаются в библиотеку work

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

library fir_lib;

use fir_lib.all;

ENTITY fir IS PORT (

date : IN std_logic_vector(3 DOWNTO 0);

reset : IN std_logic;

clk : IN std_logic;

ce : IN std_logic;

filtered : OUT std_logic_vector(9 DOWNTO 0)

);

END fir;

ARCHITECTURE STRUCTURE OF fir IS

COMPONENT fir4

port ( clk : in std_logic;

reset : in std_logic;

ce : in std_logic;

date : in std_logic_vector (3 downto 0);

q_reg : out std_logic_vector (9 downto 0));

END COMPONENT;

BEGIN

metka_fir: entity fir_lib.fir4

port map (ce=>ce,

clk=>clk,

date(3 downto 0)=>date(3 downto 0),

reset=>reset,

q_reg(9 downto 0)=>filtered(9 downto 0));

END STRUCTURE;

Пример 5. Верхний уровень иерархии проекта с использованием библиотеки fir_lib

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY test IS

END test;

ARCHITECTURE behavior OF test IS

COMPONENT fir

PORT(

date : IN std_logic_vector(3 downto 0);

reset : IN std_logic;

clk : IN std_logic;

ce : IN std_logic;

filtered : OUT std_logic_vector(9 downto 0)

);

END COMPONENT;

--Inputs

signal date : std_logic_vector(3 downto 0) := (others => '0');

signal reset : std_logic := '0';

signal clk : std_logic := '0';

signal ce : std_logic := '1';

--Outputs

signal filtered : std_logic_vector(9 downto 0);

-- Clock period definitions

constant clk_period : time := 100 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: fir PORT MAP (

date => date,

reset => reset,

clk => clk,

ce => ce,

filtered => filtered

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

reset <= '1';

end process;

tb : process

begin

wait for 100 ns;

date <= "1011";

wait for 100 ns;

date <= "0011";

wait for 100 ns;

date <= "0001";

wait for 100 ns;

date <= "0000";

wait;

end process;

END;

Пример 6. Испытательный стенд на языке VHDL для моделирования прохождения сигнала –5, 3, 1, 0 по структуре КИХ-фильтра

this_block.addFile('fir.vhd');

this_block.addFileToLibrary('fir4.vhd','fir_lib');

Пример 7. Фрагмент изменений, которые необходимо внести в m-файл fir_config, генерируемый Xilinx System Generator

Импорт проектов, созданных в САПР ПЛИС Xilinx ISE Design Suite с использованием генератора параметризированных ядер XLogiCORE IP и функции FIR Compiler v6.3

На рис. 9а показан проект КИХ-фильтра на четыре отвода в САПР ПЛИС Xilinx ISE 14.4 с использованием генератора параметризированных ядер XLogiCORE IP FIR Compiler v6.3, а на рис. 9б представлены настройки функции FIR Compiler (закладка пять, поле «сигналы управления»). Красным овалом на рис. 9 выделена пара внешних портов — clk и clken, и пара портов — aclk и aclken, принадлежащих символу fircore. Выбирается одноканальный, односкоростной (Single-Rate) систолический КИХ-фильтр прямой формы. Частота тактирования ядра фильтра установлена 250 МГц, а частота дискретизации — 50 МГц.

Рис. 9.

а) Проект КИХ-фильтра на четыре отвода в САПР ПЛИС Xilinx ISE 14.4 с использованием генератора параметризированных ядер XLogiCORE IP FIR Compiler v6.3;

б) настройки функции FIR Compiler, опционально подключается сигнал разрешения подачи синхросигнала aclken

Далее разработаем испытательный стенд (пример 8). Характерной особенностью такого КИХ-фильтра на четыре отвода является латентность в 11 тактов синхрочастоты (рис. 10).

Рис. 10. Временные диаграммы работы КИХ-фильтра на четыре отвода, созданного с использованием генератора параметризированных ядер XLogiCORE IP и функции FIR Compiler v6.3. На вход КИХ-фильтра поступают входные отсчеты –5, 3, 1 и 0. Правильные значения на выходе фильтра: 10, –1, –40, –10, 25, 6

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

LIBRARY UNISIM;

USE UNISIM.Vcomponents.ALL;

ENTITY fir4_sch_fir4_sch_sch_tb IS

END fir4_sch_fir4_sch_sch_tb;

ARCHITECTURE behavioral OF fir4_sch_fir4_sch_sch_tb IS

COMPONENT fir4_sch

PORT( s_tvalid : IN STD_LOGIC;

s_tready : OUT STD_LOGIC;

Data : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

clk : IN STD_LOGIC;

clken : IN STD_LOGIC;

m_tvalid : OUT STD_LOGIC;

filtered : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END COMPONENT;

SIGNAL s_tvalid : STD_LOGIC:= '1';

SIGNAL s_tready : STD_LOGIC;

SIGNAL Data : STD_LOGIC_VECTOR (7 DOWNTO 0):= (others => '0');

SIGNAL clk : STD_LOGIC;

SIGNAL clken : STD_LOGIC:= '1';

SIGNAL m_tvalid : STD_LOGIC;

SIGNAL filtered : STD_LOGIC_VECTOR (7 DOWNTO 0);

BEGIN

UUT: fir4_sch PORT MAP(

s_tvalid => s_tvalid,

s_tready => s_tready,

Data => Data,

clk => clk,

clken => clken,

m_tvalid => m_tvalid,

filtered => filtered

);

clk_process :process

begin

clk <= '0';

wait for 10 ns;

clk <= '1';

wait for 10 ns;

end process;

tb : process

begin

wait for 20 ns;

Data <= "11111011";

wait for 20 ns;

Data <= "00000011";

wait for 20 ns;

Data <= "00000001";

wait for 20 ns;

Data <= "00000000";

wait;

END process;

END;

Пример 8. Испытательный стенд на языке VHDL для моделирования прохождения сигнала –5, 3, 1, 0 по структуре КИХ-фильтра, созданного с использованием генератора параметризированных ядер XLogiCORE IP и функции FIR Compiler v6.3

Убедившись в том, что КИХ-фильтр работает корректно, пересохраним файл fir4_sch.vhf в файл fir4_sch.vhd (пример 9) и отредактируем его так, чтобы в нем использовалась пара сигналов с именами clk и ce (пример 10). Проанализируем полученный файл. Файл fir4_sch.vhd создан на основе компоненты fir4core, которая разработана с применением генератора параметризированных ядер XLogiCORE IP и функции FIR Compiler v6.3, а также является разновидностью структурного стиля языка VHDL. Генератор параметризированных ядер в процессе своей работы создает следующие файлы: fir4core.ngc (синтезируемая модель КИХ-фильтра, представленная списком связей на низком логическом уровне в двоичном формате, создается с помощью специального приложения Xilinx Synthesis Technology (XST), входящего в состав ISE), fir4core.mif (коэффициенты фильтра в HEX-формате) и fir4core.vhd (спецификация фильтра).

library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; library UNISIM; use UNISIM.Vcomponents.ALL; entity fir4_sch is port ( clk : in std_logic; clken : in std_logic; Data : in std_logic_vector (7 downto 0); s_tvalid : in std_logic; filtered : out std_logic_vector (7 downto 0); m_tvalid : out std_logic; s_tready : out std_logic); end fir4_sch; architecture BEHAVIORAL of fir4_sch is component fir4core port ( s_axis_data_tvalid : in std_logic; s_axis_data_tready : out std_logic; s_axis_data_tdata : in std_logic_vector (7 downto 0); aclk : in std_logic; aclken : in std_logic; m_axis_data_tvalid : out std_logic; m_axis_data_tdata : out std_logic_vector (7 downto 0)); end component; begin XLXI_1 : fir4core port map (aclk=>clk, aclken=>clken, s_axis_data_tdata(7 downto 0)=>Data(7 downto 0), s_axis_data_tvalid=>s_tvalid, m_axis_data_tdata(7 downto 0)=>filtered(7 downto 0), m_axis_data_tvalid=>m_tvalid, s_axis_data_tready=>s_tready); end BEHAVIORAL; Пример 9. Файл fir4_sch.vhd, пересохраненный из файла fir4_sch.vhf (HDL Functional Model)

library ieee; use ieee.std_logic_1164.ALL; use ieee.numeric_std.ALL; library UNISIM; use UNISIM.Vcomponents.ALL; entity fir4_sch is port ( clk : in std_logic; ce : in std_logic; Data : in std_logic_vector (7 downto 0); s_tvalid : in std_logic; filtered : out std_logic_vector (7 downto 0); m_tvalid : out std_logic; s_tready : out std_logic); end fir4_sch; architecture BEHAVIORAL of fir4_sch is component fir4core port ( s_axis_data_tvalid : in std_logic; s_axis_data_tready : out std_logic; s_axis_data_tdata : in std_logic_vector (7 downto 0); aclk : in std_logic; aclken : in std_logic; m_axis_data_tvalid : out std_logic; m_axis_data_tdata : out std_logic_vector (7 downto 0)); end component; begin XLXI_1 : fir4core port map (aclk=>clk, aclken=>ce, s_axis_data_tdata(7 downto 0)=>Data(7 downto 0), s_axis_data_tvalid=>s_tvalid, m_axis_data_tdata(7 downto 0)=>filtered(7 downto 0), m_axis_data_tvalid=>m_tvalid, s_axis_data_tready=>s_tready); end BEHAVIORAL; Пример 10. Отредактированный файл fir4_sch.vhd, в котором используется пара сигналов с именами clk и ce

Далее разработаем имитационную модель на основе функционального блока Black Box c использованием файла fir4_sch.vhd (рис. 11, 12). На рис. 11 показано, что профильтрованный сигнал подвергается децимации. Блок децимации выполняет роль компрессора. В выходном сигнале сохраняются отсчеты с номерами, кратными четырем. Такой прием позволяет сэкономить вычислительные ресурсы ПЛИС. Функциональный блок Black Box сгенерирует m‑файл с именем fir4_sch_config (пример 11), который должен быть отредактирован. Помимо ссылок на файл fir4_sch.vhd, в него должны быть добавлены ссылки на файлы fir4core.ngc, fir4core.mif и fir4core.vhd.

Рис. 11. Имитационная модель КИХ-фильтра на четыре отвода для реализации в базисе ПЛИС серии Spartan 6 xa6slx4-3tqg144 на основе функционального блока Black Box c использованием файла fir4_sch.vhd, созданного на основе компоненты fir4core

Рис. 12. Имитационное моделирование в системе Matlab/Simulink КИХ-фильтра на четыре отвода на основе функционального блока Black Box c использованием файла fir4_sch.vhd, созданного на основе компоненты fir4core

function fir4_sch_config(this_block)

this_block.setTopLevelLanguage('VHDL');

this_block.setEntityName('fir4_sch');

this_block.tagAsCombinational;

this_block.addSimulinkInport('Data');

this_block.addSimulinkInport('s_tvalid');

this_block.addSimulinkOutport('filtered');

this_block.addSimulinkOutport('m_tvalid');

this_block.addSimulinkOutport('s_tready');

filtered_port = this_block.port('filtered');

filtered_port.setType('Fix_8_0');

m_tvalid_port = this_block.port('m_tvalid');

m_tvalid_port.setType('UFix_1_0');

m_tvalid_port.useHDLVector(false);

s_tready_port = this_block.port('s_tready');

s_tready_port.setType('UFix_1_0');

s_tready_port.useHDLVector(false);

if (this_block.inputTypesKnown)

if (this_block.port('Data').width ~= 8);

this_block.setError('Input data type for port "Data" must have width=8.');

end

if (this_block.port('s_tvalid').width ~= 1);

this_block.setError('Input data type for port "s_tvalid" must have width=1.');

end

this_block.port('s_tvalid').useHDLVector(false);

end

if (this_block.inputRatesKnown)

setup_as_single_rate(this_block,'clk','ce')

end

uniqueInputRates = unique(this_block.getInputRates);

this_block.addFile('fir4core.vhd');

this_block.addFile('fir4core.ngc');

this_block.addFile('fir4core.mif');

this_block.addFile('fir4_sch.vhd');

return;

function setup_as_single_rate(block,clkname,cename)

inputRates = block.inputRates;

uniqueInputRates = unique(inputRates);

if (length(uniqueInputRates)==1 & uniqueInputRates(1)==Inf)

block.addError('The inputs to this block cannot all be constant.');

return;

end

if (uniqueInputRates(end) == Inf)

hasConstantInput = true;

uniqueInputRates = uniqueInputRates(1:end-1);

end

if (length(uniqueInputRates) ~= 1)

block.addError('The inputs to this block must run at a single rate.');

return;

end

theInputRate = uniqueInputRates(1);

for i = 1:block.numSimulinkOutports

block.outport(i).setRate(theInputRate);

end

block.addClkCEPair(clkname,cename,theInputRate);

return;

Пример 11. Отредактированный m-файл, созданный на основе файла fir4_sch.vhd

Выводы

Использование методологии Black Boxes Xilinx System Generator значительно повышает возможности объектно-ориентированного проектирования при разработке имитационных моделей цифровых устройств для реализации в базисе ПЛИС, так как позволяет импортировать коды высокоуровневых языков описания аппаратурных средств из САПР Xilinx ISE в систему Matlab/Simulink, полученных с помощью различных приемов.

- Строгонов А., Цыбин С., Городков П. Проектирование КИХ-фильтров в САПР ПЛИС Xilinx ISE Design Suite // Компоненты и технологии. 2014. № 11.

- Строгонов А., Цыбин С., Городков П. Проектирование КИХ-фильтров на распределенной арифметике в САПР ПЛИС Xilinx ISE Design Suite // Компоненты и технологии. 2015. № 2.

- Строгонов А., Цыбин С., Городков П. Разработка КИХ-фильтров в системе Xilinx System Generator САПР ISE Design Suite // Компоненты и технологии. 2015. № 5.

- Строгонов А., Цыбин С., Городков П. Проектирование последовательных КИХ-фильтров в системе Xilinx System Generator с применением библиотеки Reference BlockSet/DSP // Компоненты и технологии. 2015. № 6.

- System Generator for DSP User Guide. UG640 (v 13.3). October 19, 2011.

- Тарасов И. Использование САПР PlanAhead для разработки цифровых систем на базе ПЛИС Xilinx // Компоненты и технологии. 2012. № 4.

4 августа, 2020

4 августа, 2020 27 июня, 2022

27 июня, 2022 14 февраля, 2022

14 февраля, 2022